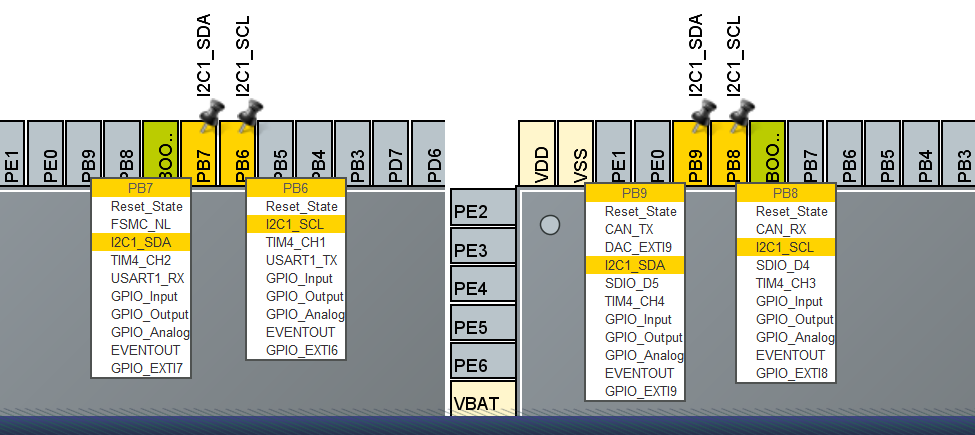

GPIO در STM32 به مفهوم مجموعۀ پایه های ورودی/خروجی به همراه تمامی مدهای عملکرد آنهاست. GPIO مخفف عبارت General-purpose input/output به معنی ورودی/خروجی همه منظوره است. واحد GPIO در STM32 در سری های مختلف دارای تعداد پورت ها و پایه ها و عملکردهای متفاوت است. پورت های ورودی/خروجی با حروف انگلیسی A و B و C و … نام گذاری شده اند. و هر پورت می تواند حداکثر 16 پایه داشته باشد. در میکروکنترلرهای STM32، عملکردهای مربوط به پورت های I/O که شامل خواندن مقادیر دیجیتال از آنها یا نوشتن مقادیر دیجیتال روی آنهاست، با عملکردهای مربوط به واحدهای دیگر تلفیق شده و نام GPIO را به خود گرفته است. در برخی سری های این میکروکنترلرها مثل سری STM32F101/2/3/5/7xx، این واحد، GPIO and AFIO نام دارد. AFIO مخفف عبارت Alternate function input/output به معنی ورودی/خروجی عملکردهای دیگر است. در واقع هر پایۀ میکروکنترلر علاوه بر عملکرد ورودی/خروجی در پورت، می تواند توسط دیگر واحدهای داخلی به کار گرفته شود. برای این کار باید پایۀ مورد نظر در مد Alternate function یا AF پیکربندی شود. نکتۀ مورد توجه این است که پیش از فعال کردن یک واحد داخلی که نیاز به پایۀ ورودی/خروجی دارد، باید مد آن پایه توسط رجیسترهای GPIO، روی AF تنظیم شود. فرض کنید می خواهیم یک پروتکل I2C را در STM32F103VET6 توسط واحد I2C1 راه اندازی کنیم. در این صورت باید پایه های PB6 و PB7 یا PB8 و PB9 را قبل از راه اندازی I2C1 در مد صحیح پیکربندی کنیم. این دو پایه را که خطوط SCL و SDA واحد I2C1 هستند، باید در مد AF در حالت Open-drain تنظیم کنیم.

تصویر 1 – عملکردهای دیگر پایه های PB6 تا PB9 در STM32F103VET6 و انتخاب عملکرد واحد I2C1 برای آنها

در این نوشته به واحد GPIO در STM32 برای سری های زیر می پردازیم:

| STM32MP157 | STM32L4+ | STM32F0x1

STM32F0x2 STM32F0x8 |

STM32F101xx

STM32F102xx STM32F103xx STM32F105xx STM32F107xx |

| STM32G0x1 | STM32H742xx

STM32H743/53xx STM32H750xB |

STM32F334xx | STM32F205xx

STM32F207xx STM32F215xx STM32F217xx |

| STM32WB55xx

STM32WB35xx |

STM32F75xxx

STM32F74xxx |

STM32F405xx/07xx

STM32F415xx/17xx STM32F42xxx STM32F43xxx |

جدول 1 – المان های مورد بحث این نوشته

بنابراین هر جایی از نوشته که می گوییم “GPIO در STM32″، منظور ما سری های مذکور است. با این که در یک نوشته نمی توان به GPIO همۀ میکروکنترلرهای STM32 پرداخت، اما مطالب این نوشته برای یادگیری GPIO سری های دیگر کافی است.

نکته: سری STM32WB55/35xx میکروکنترلرهای مخصوص ارتباطات بی سیم هستند که چند پروتکل ارتباطی را پشتیبانی می کنند. همچنین STM32MP157 یک میکروپروسسور است و لازم دانستیم در این نوشته مباحث مربوط به GPIO آن را بررسی کنیم.

نکته: در این نوشته مطالب جامعی دربارۀ GPIO در STM32 آمده است. اختصاص زمان کافی برای مطالعۀ دقیق این مطالب و سعی در یادگیری آنها، درک عمیق از واحد GPIO در میکروکنترلرهای STM32 را نتیجه می دهد. ممکن است برخی مطالب، مورد نیاز افرادی که کار با این میکروکنترلرها را به تازگی شروع کرده اند، نباشد. بنابراین این افراد می توانند خواندن مطالب مربوط به پیکربندی GPIO در مدهای مختلف، مشخصات الکتریکی و زمانی و همچنین امکاناتی مثل قفل پیکربندی را به زمان دیگری موکول نمایند.

در ادامه ابتدا به بلوک دیاگرام GPIO در STM32 می پردازیم. سپس مدهای GPIO را بیان می کنیم و پیکربندی GPIO را برای هر مد شرح می دهیم. بعد از آن به مشخصات الکتریکی و زمانی GPIO می پردازیم. سپس با ذکر چند نکته، چند مفهوم مهم GPIO از جمله قفل پیکربندی GPIO در STM32 را شرح می دهیم. در نهایت رجیسترهای GPIO را بررسی می کنیم.

برای مطالعۀ یک پروژه GPIO در STM32 می توانید به نوشتۀ «راه اندازی سون سگمنت با STM32» مراجعه نمایید.

تصویر 2 – راه اندازی سون سگمنت با STM32

بلوک دیاگرام GPIO در STM32

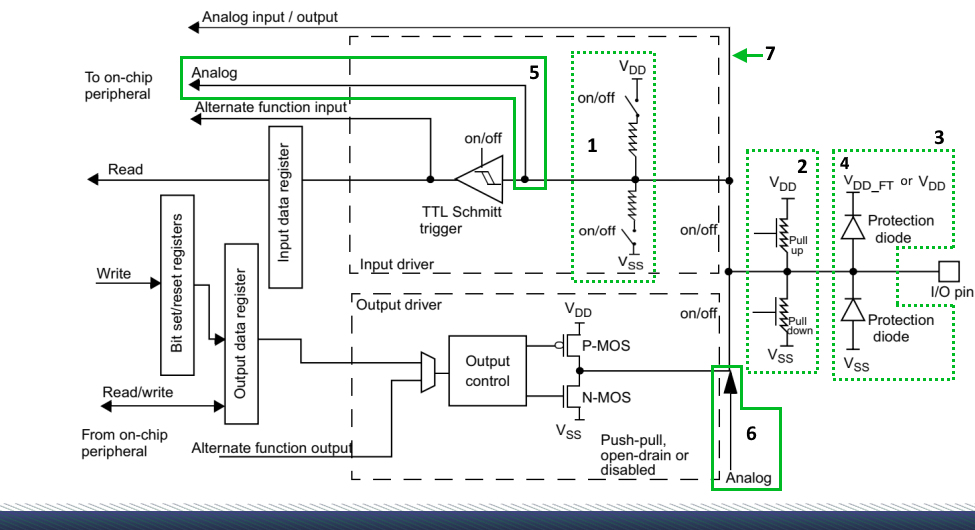

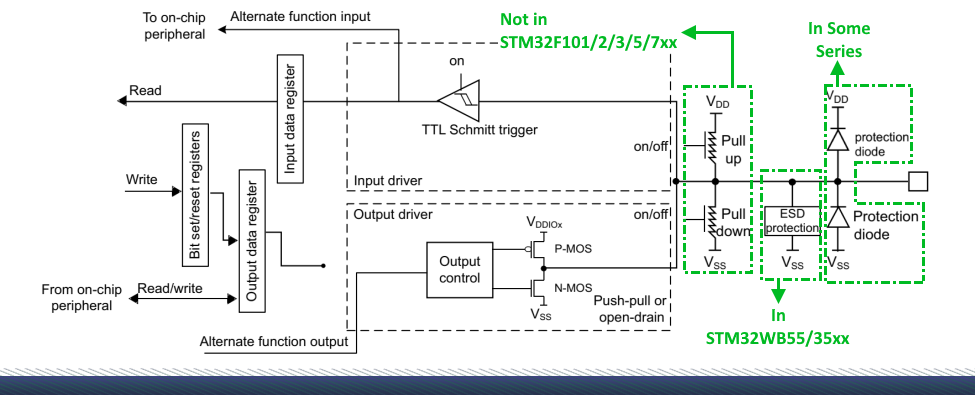

بلوک دیاگرام پایه های GPIO در STM32 در سری های مختلف، تفاوت هایی با هم دارند. به طور کلی بخش های اصلی هر پایه از پورت های GPIO عبارتند از:

- دیودهای محافظ: که در برخی سری ها ممکن است وجود نداشته باشند؛

- مقاومت های پول آپ و پول دون: که در برخی سری ها در بخش درایور ورودی و در برخی دیگر، در کنار دیودهای محافظ هستند؛

- درایور ورودی: که شامل یک اشمیت تریگر و گاهی مقاومت های پول آپ و پول دون است؛

- درایور خروجی: که شامل کنترل کنندۀ خروجی و ترانزیستورهای N-MOS و P-MOS است.

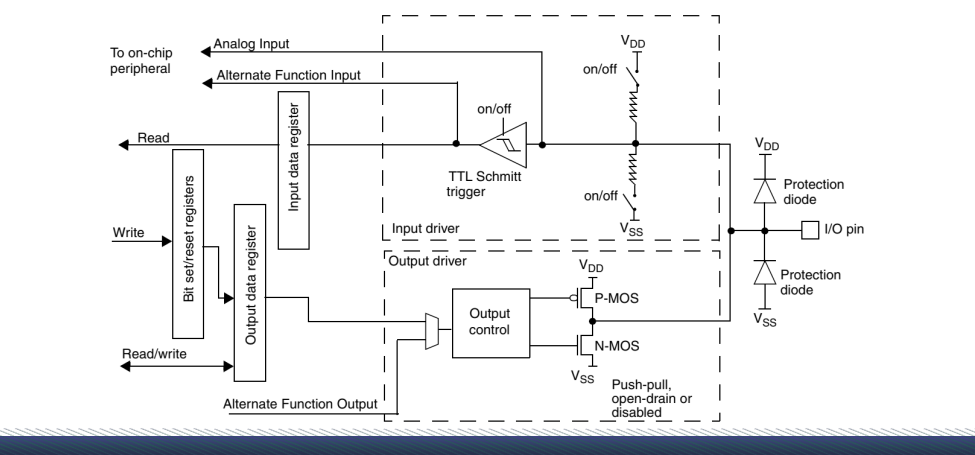

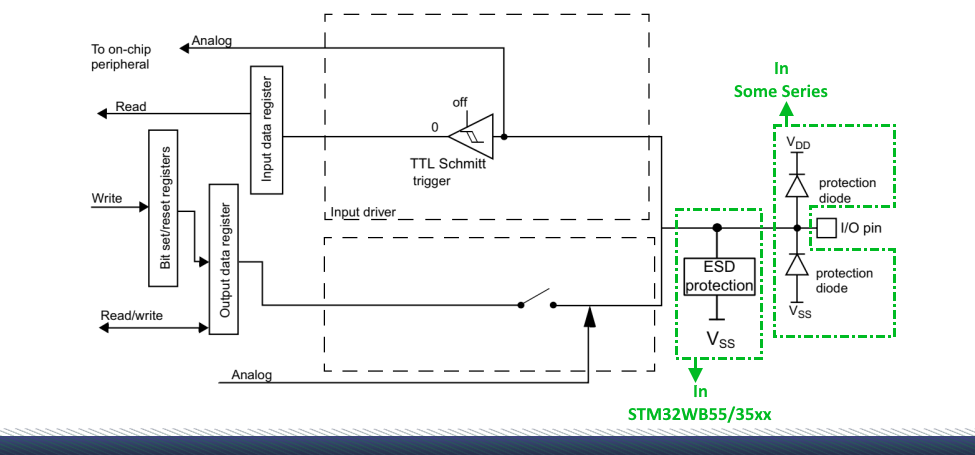

بلوک دیاگرام GPIO در STM32 را برای سری های مورد بحث این نوشته (به جز سری STM32WB55/35xx و STM32WB35xx)، می توان در تصویر زیر خلاصه کرد.

تصویر 3 – بلوک دیاگرام GPIO در STM32

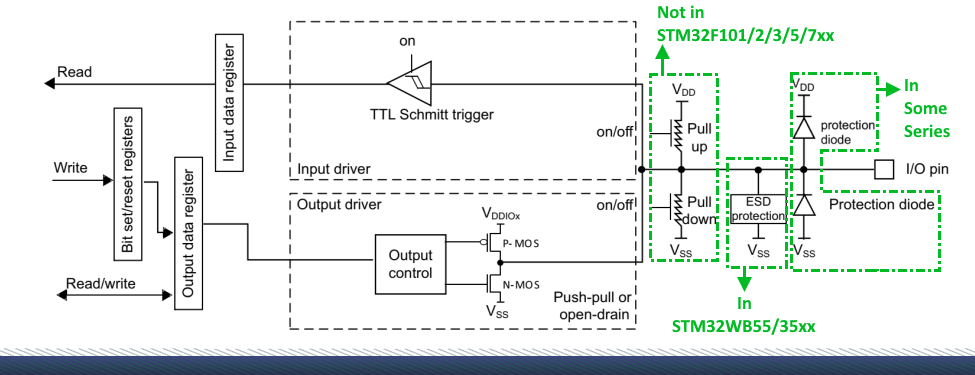

در برخی سری ها مثل STM32F101/2/3/5/7xx، مقاومت های پول آپ و پول دون در بخش درایور ورودی و قبل از اشمیت تریگر قرار دارد (1). در بسیاری دیگر، مکان این مقاومت های پول آپ و پول دون در کنار دیودهای محافظ است (2). در بلوک دیاگرام GPIO برخی سری ها دیودهای محافظ وجود ندارد (3). در برخی سری ها GPIO قابلیت p5-Volt tolerant را دارد. در این موارد کاتد دیود محافظ بالایی، به جای اتصال به VDD، به VDD FT متصل است (4). همچنین در بلوک دیاگرام برخی سری ها، مسیر ورودی آنالوگ، از ورودی اشمیت تریگر گرفته شده است (5). مسیر خروجی آنالوگ نیز مستقیماً به پایه متصل شده است (6). در برخی دیگر، ورودی و خروجی آنالوگ به این شکل نیست. و روی یک خط به صورت ورودی /خروجی متصل به پایه رسم شده است (7).

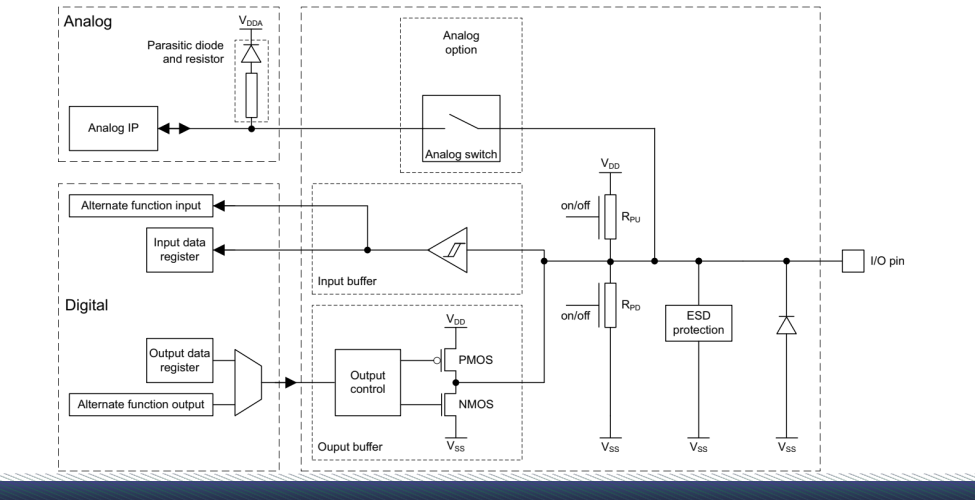

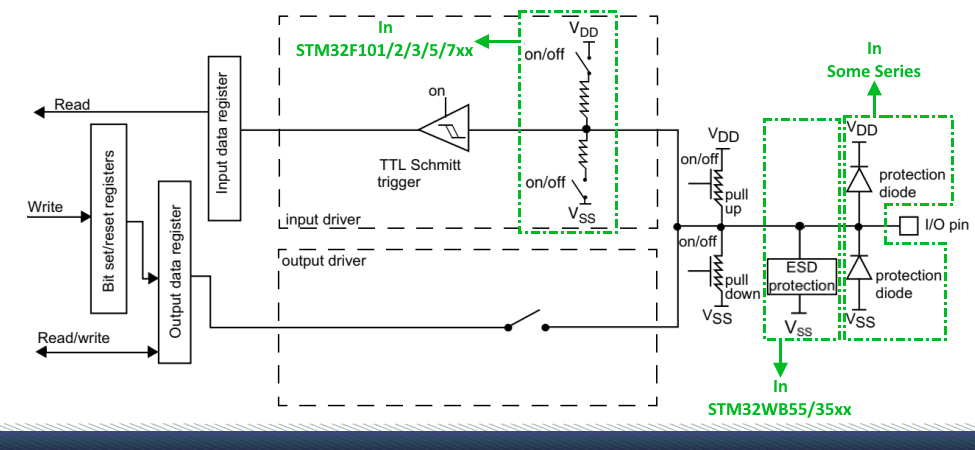

بلوک دیاگرام GPIO در STM32WB55xx و STM32WB35xx به صورت تصویر زیر است. از تفاوت های اصلی بلوک دیاگرام GPIO این سری با سری های قبل، وجود حفاظت ESD است.

تصویر 4 – بلوک دیاگرام GPIO در STM32WB55xx و STM32WB35xx

مدهای GPIO در STM32

این مدها حاصل فعال سازی یا غیر فعال سازی مقاومت های پول آپ و پول دون، پوش پول یا Open-drain بودن درایور خروجی و استفاده از ورودی/خروجی آنالوگ و AFIO است. در GPIO میکروکنترلرهای STM32 در بخش ورودی، هم مقاومت پول آپ و هم مقاومت پول دون وجود دارد. همچنین در سری هایی که مقاومت های پول آپ و پول دون در بخش درایور ورودی نیست، این مقاومت ها می توانند به همراه درایور خروجی در حالت های پوش پول و Open-drain فعال شوند. در مدهای AFO نیز پایه ها می توانند به صورت پوش پول یا Open-drain به همراه پول آپ یا پول دون یا بدون آنها باشند. در سری های مورد بحث این نوشته (به جز STM32F101/2/3/5/7xx)، مدهای GPIO به صورت جدول زیر است.

| I/O configuration | PUPDR(i) [1:0] | OSPEEDR(i) [B:A] | OTYPER (i) | MODER(i) [1:0] | |||

| PP | GP output | 0 | 0 | SPEED [B:A] | 0 | 01 | |

| PP+PU | GP output | 1 | 0 | 0 | |||

| PP+PD | GP output | 0 | 1 | 0 | |||

| Reserved | 1 | 1 | 0 | ||||

| OD | GP output | 0 | 0 | 1 | |||

| OD+PU | GP output | 1 | 0 | 1 | |||

| OD+PD | GP output | 0 | 1 | 1 | |||

| Reserved | 1 | 1 | 1 | ||||

| PP | AF | 0 | 0 | 0 | 10 | ||

| PP+PU | AF | 1 | 0 | 0 | |||

| PP+PD | AF | 0 | 1 | 0 | |||

| Reserved | 1 | 1 | 0 | ||||

| OD | AF | 0 | 0 | 1 | |||

| OD+PU | AF | 1 | 0 | 1 | |||

| OD+PD | AF | 0 | 1 | 1 | |||

| Reserved | 1 | 1 | 1 | ||||

| Floating | Input | 0 | 0 | x | x | x | 00 |

| PU | Input | 1 | 0 | x | x | x | |

| PD | Input | 0 | 1 | x | x | x | |

| Reserved (input floating) | 1 | 1 | x | x | x | ||

| Analog | Input/output | 0 | 0 | x | x | x | 11 |

| Reserved | 1 | 0 | x | x | x | ||

| 0 | 1 | x | x | x | |||

| 1 | 1 | x | x | x | |||

| GP = general-purpose, PP = push-pull, PU = pull-up, PD = pull-down, OD = open-drain, AF = alternate function. | |||||||

جدول 2 – مدهای GPIO در STM32، سری های به جز STM32F101/2/3/5/7xx

تصویر 5 – بلوک دیاگرام GPIO در STM32، مقاومت پول آپ و پول دون در کنار دیود محافظ

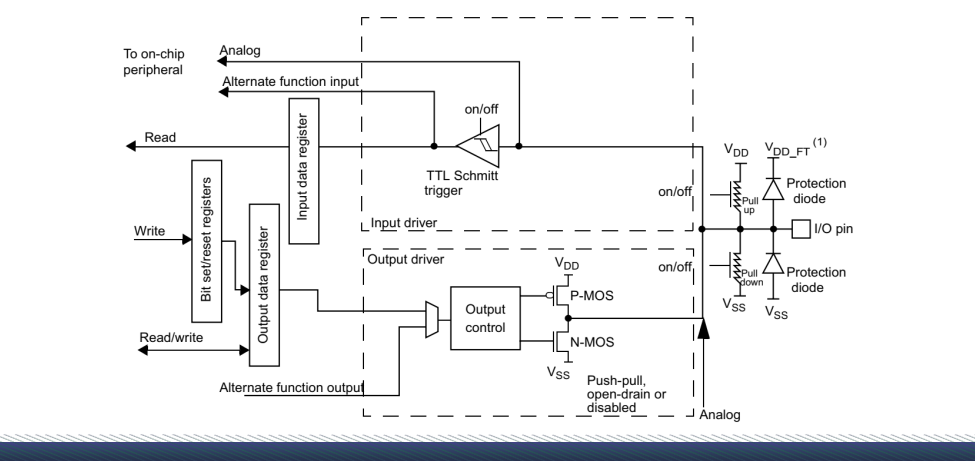

مدهای GPIO در STM32F101/2/3/5/7xx

در این سری مقاومت های پول آپ و پول دون در بخش درایور ورودی قرار دارند. این مقاومت ها تنها در مدهای ورودی فعال می شوند. بنابراین تعداد مدهایی که به وجود می آید، کمتر از مدهایی است که در بخش قبل بررسی کردیم. در این سری خروجی می تواند به صورت پوش پول یا Open-drain باشد. در هردوی حالات مذکور مقاومت های پول آپ و پول دون وجود ندارد. هر پایه در مدهای ورودی می تواند دارای مقاومت پول آپ، پول دون یا بدون آنها باشد. در مدهای AFO، پایه ها می توانند پوش پول یا Open-drain بدون مقاومت های پول آپ و پول دون باشند. در این سری، مد آنالوگ در گروه مدهای ورودی قرار دارد. مدهای GPIO در STM32F101/2/3/5/7xx به صورت جدول زیر است.

| PxODR | MODE0 | MODE1 | CNF0 | CNF1 | Configuration mode | |

| 0 or 1 | MODE[1:0] | 0 | 0 | Push-pull | GP Output | |

| 0 or 1 | 1 | Open-drain | ||||

| Don’t care | 0 | 1 | Push-pull | AF output | ||

| Don’t care | 1 | Open-drain | ||||

| Don’t care | 00 | 0 | 0 | Analog | Input | |

| Don’t care | 1 | Floating | ||||

| 0 | 0 | 1 | Pull-down | |||

| 1 | Pull-up | |||||

جدول 3 – مدهای GPIO در STM32، سری STM32F101/2/3/5/7xx

نکته: پیکربندی مدهای GPIO در سری STM32F101/2/3/5/7xx با مقداردهی به رجیسترهای CR و ODR انجام می شود. CNF و MODE بیت های رجیسترهای CR هستند و بیت های ODR نیز خود رجیستر ODR را شکل می دهند. در این سری، بیت های MODE تعیین کنندۀ سرعت خروجی هستند. در سری های دیگر، هر یک از بیت های MODER و OTYPER و OSPEEDR و PUPDR، رجیستر جداگانه ای دارند. همچنین در سری STM32F101/2/3/5/7xx رجیستر ODR تعیین کنندۀ وجود یا عدم وجود مقاومت های پول آپ و پول دون است. اما در سری های دیگر، برای مقاومت های پول آپ و پول دون، رجیستر جداگانه یعنی PUPDR وجود دارد.

تصویر 6 – بلوک دیاگرام GPIO در STM32، سری STM32F101/2/3/5/7xx

پیکربندی GPIO در STM32 در مدهای مختلف

در هر یک از مدهای ورودی، خروجی، AF و آنالوگ، بخش هایی از واحد GPIO، فعال و بخش هایی دیگر غیر فعال است. این بخش ها شامل بافر خروجی، ورودی اشمیت تریگر و مقاومت های پول آپ و پول دون هستند. وقتی یک پایه در یکی از مدهای ورودی است:

- بافر خروجی غیر فعال است.

- ورودی اشمیت تریگر فعال است.

- مقاومت های پول آپ و پول دون بسته به مقدار رجیستر مربوط فعال یا غیر فعال هستند. (در STM32F101/2/3/5/7xx، رجیستر ODR و در باقی سری ها، رجیستر PUPDR)

- با هر سیکل کلاک AHB (یا APB2در سری STM32F101/2/3/5/7xx)، از وضعیت روی پایۀ ورودی، یک نمونه گرفته و در رجیستر IDR ذخیره می شود.

- با خواندن رجیستر IDR، وضعیت قرار گرفته روی پایۀ ورودی خوانده می شود.

تصویر 7 – پیکربندی GPIO در مد Input

وقتی یک پایه در یکی از مدهای خروجی است:

- بافر خروجی فعال است و الف) در مد Open-drain، مقدار صفر در ODR ترانزیستور N-MOS را فعال و مقدار یک در آن، پایه را امپدانس بالا می کند. در این حالت ترانزیستور P-MOS فعال نمی شود. ب) در مد پوش پول، مقدار صفر در ODR ترانزیستور N-MOS را فعال و مقدار یک در آن، ترانزیستور P-MOS را فعال می کند.

- ورودی اشمیت تریگر فعال است.

- مقاومت های پول آپ و پول دون بسته به مقدار PUPDR، فعال یا غیر فعال هستند. در سری STM32F101/2/3/5/7xx این مقاومت ها غیر فعال هستند.

- با هر سیکل کلاک AHB (یا APB2 در سری STM32F101/2/3/5/7xx)، از مقدار روی پایۀ خروجی، یک نمونه گرفته و در IDR ذخیره می شود.

- با خواندن IDR، وضعیت پایه خوانده می شود. در سری STM32F101/2/3/5/7xx، با خواندن IDRدر مد Open-drain، وضعیت روی پایه خوانده می شود.

- با خواندن ODR، آخرین مقدار نوشته شده، خوانده می شود. در سری STM32F101/2/3/5/7xx، با خواندن ODRدر مد پوش پول، آخرین مقدار نوشته شده، خوانده می شود.

تصویر 8 – پیکربندی GPIO در مد Output

پیکربندی GPIO در STM32 در مدهای AF و آنالوگ

هنگامی که یک پایه در مد AF است:

- بافر خروجی می تواند در مدهای Open-drain یا پوش پول پیکربندی شود.

- بافر خروجی با سیگنالی که از سمت واحد داخلی می آید، راه اندازی می شود.

- ورودی اشمیت تریگر فعال است.

- مقاومت های پول آپ و پول دون بسته به مقدار PUPDR، فعال یا غیر فعال هستند. در سری STM32F101/2/3/5/7xx مقاومت های پول آپ و پول دون غیر فعال هستند.

- با هر سیکل کلاک AHB (یا APB2 در سری STM32F101/2/3/5/7xx)، از وضعیت روی پایه، یک نمونه گرفته و در IDR ذخیره می شود.

- با خواندن رجیستر IDR، وضعیت روی پایه خوانده می شود. در سری STM32F101/2/3/5/7xx، با خواندن IDRدر مد Open-drain، وضعیت روی پایه خوانده می شود.

- در سری STM32F101/2/3/5/7xx، با خواندن ODRدر مد پوش پول، آخرین مقدار نوشته شده، خوانده می شود.

تصویر 9 – پیکربندی GPIO در مد Alternate function

نکته: هنگامی که پایه برای یک عملکرد LCD تنظیم شود، پیکربندی AF اینگونه که توضیح داده شد، برای آن اعمال نمی شود. بلکه پیکربندی آن مطابق پیکربندی مد آنالوگ اعمال می شود. این موضوع برای سری STM32WB55/35xx که یک واحد داخلی برای راه اندازی نمایشگر LCD نوع TFT دارد، صادق است.

زمانی که یک پایه در مد آنالوگ است:

- بافر خروجی غیر فعال است.

- ورودی اشمیت تریگر غیر فعال است و مصرف صفر را برای هر مقدار آنالوگ روی پایه تأمین می کند. خروجی اشمیت تریگر در سطح صفر نگه داشته می شود.

- مقاومت های پول آپ و پول دون غیر فعال هستند.

- با خواندن رجیستر IDR، مقدار صفر خوانده می شود.

نکته: در پیکربندی آنالوگ، پایه قابلیت p5-Volt tolerantرا ندارد.

تصویر 10 – پیکربندی GPIO در مد Analog

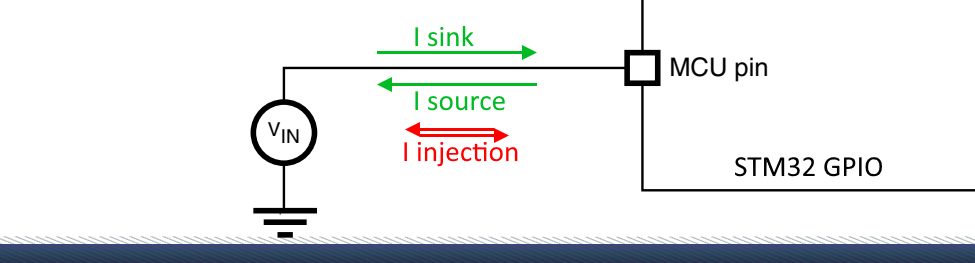

مشخصات الکتریکی و زمانی GPIO در STM32

مشخصات الکتریکی GPIO در STM32 برای میکروکنترلرهای مختلف در دیتاشیت آن میکروکنترلر آمده است. بررسی دیتاشیت همۀ میکروکنترلرهای سری های مورد بحث، امکان پذیر نیست. بنابراین تنها به مشخصات GPIO میکروکنترلرهای STM32F103xC/D/E می پردازیم. حداکثر مقدار مطلق برای ولتاژ اعمالی به یک پایۀ ورودی، جریان های Sink و Source و همچنین مقدار جریان Injection پایه ها به صورت جدول زیر است. جریان Injection زمانی به وجود می آید که ولتاژ اعمال شده به پایه، از VSS کمتر یا از VDD بیشتر باشد.

| Unit | Max | Min | Ratings | Symbol |

| V | VDD+0.4 | VSS-0.3 | Input voltage on five volt tolerant pin | VIN |

| 4 | VSS-0.3 | Input voltage on any other pin | ||

| mA | 25 | – | Output current sunk by any I/O and control pin | II/O |

| -25 | – | Output current source by any I/Os and control pin | ||

| -5/+0 | – | Injected current on five volt tolerant pins | IINJ(PIN) | |

| ±5 | – | Injected current on any other pin | ||

| ±25 | – | Total injected current (sum of all I/O and control pins) | ITINJ(PIN) |

جدول 4 – مقادیر مطلق ولتاژ ورودی و جریان پایه های GPIO در STM32

تصویر 11 – پایۀ GPIO در STM32 و جریان های Sink و Source و Injection و ولتاژ ورودی

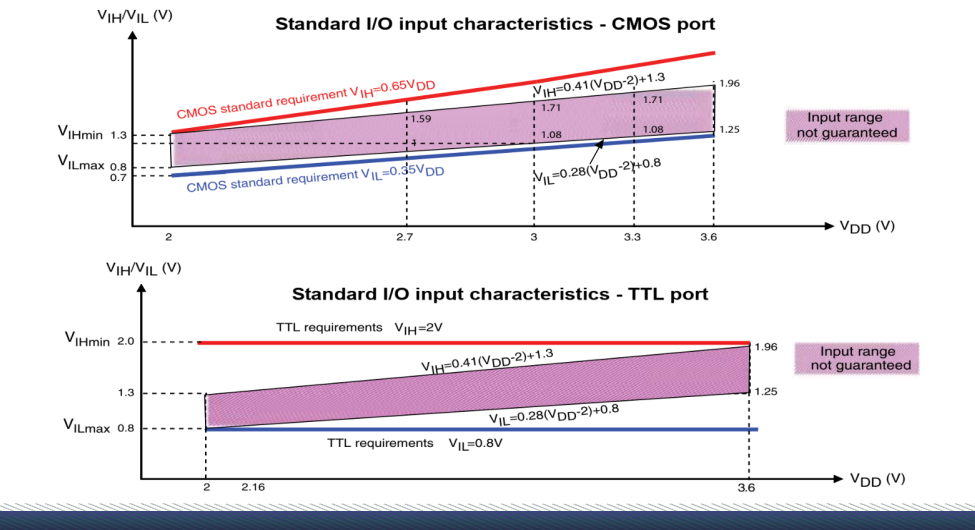

مشخصات الکتریکی ورودی/خروجی

در جدول زیر مشخصات عمومی پایه های GPIO در شرایط عملیاتی (Operation condition) آمده است. توجه شود که FT به معنای p5-Volt tolerant است. همچنین اگر جریان Injection منفی در پایه های مجاور وجود داشته باشد، جریان نشتی (Ilkg) ممکن است از مقدار ماکزیمم نوشته شده برای آن بیشتر شود. جریان Injection منفی زمانی به وجود می آید که VIN کمتر از VSS باشد.

| Unit | Max | Typ | Min | Conditions | Parameter | Symbol |

| V | 0.28*(VDD-2)+0.8 | – | -0.3 | – | Standard I/O input low level voltage | VIL |

| V | 0.32*(VDD-2)+0.75 | – | -0.3 | I/O FT input low level voltage | ||

| V | VDD+0.3 | – | 0.41*(VDD-2 V)+1.3 V | – | Standard I/O input high level voltage | VIH |

| V | 5.5 | – | 0.42*(VDD-2 V)+1 V | VDD > 2 V | I/O FT input high level voltage | |

| V | 5.2 | VDD ≤ 2 V | ||||

| mA | ±3 | – | – | – | Sink or source current of PC13, PC14, PC15 | II/O |

| mA | ±8 | – | – | – | Sink or source current of any other pins | |

| mA | ±20 | – | – | Relaxd VOL/VOH | Sink or source current of any other pins | |

| mV | – | – | 200 | – | Standard I/O Schmitt trigger voltage hysteresis | Vhys |

| mV | – | – | 5% VDD | I/O FT Schmitt trigger voltage hysteresis | ||

| uA | ±1 | – | – | VSS ≤ VIN ≤ VDD Standard I/Os | Input leakage current | Ilkg |

| 3 | – | – | VIN=5V I/O FT | |||

| kΩ | 50 | 40 | 30 | VIN=VSS | Weak pull-up equivalent resistor | RPU |

| kΩ | 50 | 40 | 30 | VIN=VDD | Weak pull-down equivalent resistor | RPD |

| pF | – | 5 | – | – | I/O pin capacitance | CI/O |

جدول 5 – مشخصات الکتریکی پایه های GPIO در STM32

جریان مصرفی پورت های GPIO بر حسب فرکانس نیز به صورت زیر است.

| Unit | Current consumption | Peripheral | |

| uA/MHz | 8,47 | GPIOA | APB2 (up to 72 MHz) |

| 8,47 | GPIOB | ||

| 6,53 | GPIOC | ||

| 8,47 | GPIOD | ||

| 6,53 | GPIOE | ||

| 6,53 | GPIOF | ||

| 6,11 | GPIOG | ||

جدول 6 – جریان مصرفی پورت های I/O در STM32

تصویر 12 – مشخصات الکتریکی ورودی پایه های ورودی/خروجی استاندارد

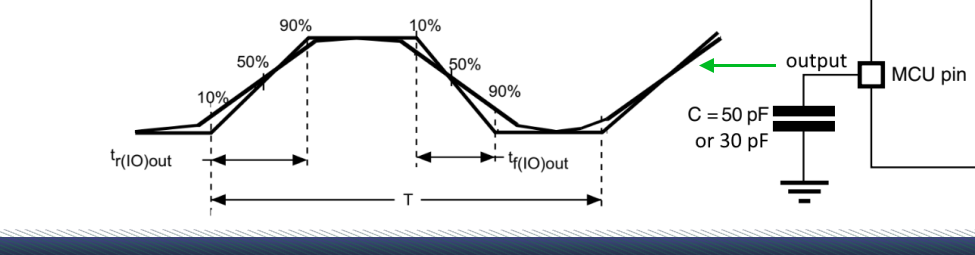

مشخصات زمانی GPIO در STM32

مشخصات AC پایه های GPIO به صورت جدول زیر است. توجه شود که در STM32F103xC/D/E، بیت های MODE1 و MODE0، حداکثر سرعت پایه را مشخص می کنند.

| Unit | Max | Min | Conditions | Parameter | Symbol | MODE [1:0] |

| MHz | 2 | – | CL = 50 pF, VDD = 2 V to 3.6 V | Maximum frequency | fmax(I/O)out | 10 |

| ns | 125 | – | Output high to low level fall time | tf(I/O)out | ||

| ns | 125 | – | Output low to high level rise time | tr(I/O)out | ||

| MHz | 10 | – | CL = 50 pF, VDD = 2 V to 3.6 V | Maximum frequency | fmax(I/O)out | 1 |

| ns | 25 | – | Output high to low level fall time | tf(I/O)out | ||

| ns | 25 | – | Output low to high level rise time | tr(I/O)out | ||

| MHz | 50 | – | CL = 30 pF, VDD = 2.7 V to 3.6 V | Maximum frequency | fmax(I/O)out | 11 |

| MHz | 30 | CL = 50 pF, VDD = 2.7 V to 3.6 V | ||||

| MHz | 20 | – | CL = 50 pF, VDD = 2 V to 2.7 V | |||

| ns | 5 | – | CL = 30 pF, VDD = 2.7 V to 3.6 V | Output high to low level fall time | tf(I/O)out | |

| ns | 8 | – | CL = 50 pF, VDD = 2.7 V to 3.6 V | |||

| ns | 12 | – | CL = 50 pF, VDD = 2 V to 2.7 V | |||

| ns | 5 | – | CL = 30 pF, VDD = 2.7 V to 3.6 V | Output low to high level rise time | tr(I/O)out | |

| ns | 8 | – | CL = 50 pF, VDD = 2.7 V to 3.6 V | |||

| ns | 12 | – | CL = 50 pF, VDD = 2 V to 2.7 V | |||

| ns | – | 10 | – | Pulse width of external signals detected by the EXTI controller | tEXTIpw | – |

جدول 7 – مشخصات AC پایه های GPIO در STM32

تصویر 13 – سیگنال پایۀ GPIO در STM32 در مدهای خروجی روی بار خازنی

نکات GPIO در STM32

در این بخش به ذکر نکاتی مهم می پردازیم:

- این امکان وجود دارد که رجیسترهای مربوط به پیکربندی پایه ها را قفل کنیم. این کار با رجیستر LCKR انجام می شود. با فعال کردن بیت های این رجیستر، بیت های مرتبط با پایۀ مورد نظر در جیسترهای MODER و OTYPER و OSPEEDR و PUPDR و AFRL و AFRH فریز می شوند. در سری STM32F101/2/3/5/7xx بیت های مرتبط، در رجیسترهای CRL و CRH فریز می شوند. بیت های فریز شدۀ این رجیسترها تا ریست بعدی میکروکنترلر یا GPIO، قابل تغییر نخواهند بود.

- در سری STM32F101/2/3/5/7xx حداکثر سرعت خروجی را 2 یا 10 یا 50 مگاهرتز تعیین می کنیم. در سری های دیگر این ارقام وجود ندارد و به جای آنها از عباراتی مانند Low Speed و Medium Speed و High Speed و … استفاده می شود. در جدول مشخصات AC در دیتاشیت، به ازای ولتاژهای VDD مختلف و شرایط دیگر، مقادیر مختلفی برای سرعت پایۀ خروجی آورده شده است.

- در برخی سری ها یک بخش به اسم I/O Compensation Cell (سلول جبران I/O) وجود دارد. کاربرد آن، کاهش Slew rate سیگنال روی پایۀ خروجی و درنتیجه کاهش اثر نویز روی تغذیه است. این سلول باید در سرعت های مشخص پایه های GPIO به ازای ولتاژهای مشخص فعال شود. سری های STM32F205/07/15/17xx و STM32F405/07/15/17xx و STM32F42/43xxx و STM32F75/74xxx و STM32H742/43/53xx و STM32H750xB و STM32MP157 دارای این سلول هستند.

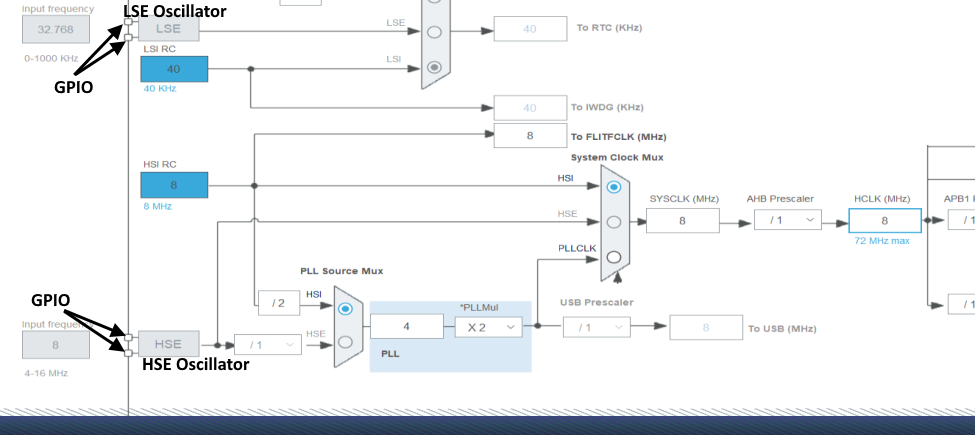

- در صورت خاموش بودن اسیلاتورهای LSE و HSE، می توان پایه های مربوط به اتصال کریستال آنها را به عنوان GPIO استفاده کرد.

تصویر 14 – اسیلاتورهای LSE و HSE غیر فعال و پایه های کریستال آنها به عنوان GPIO

نکات مربوط به Alternate function

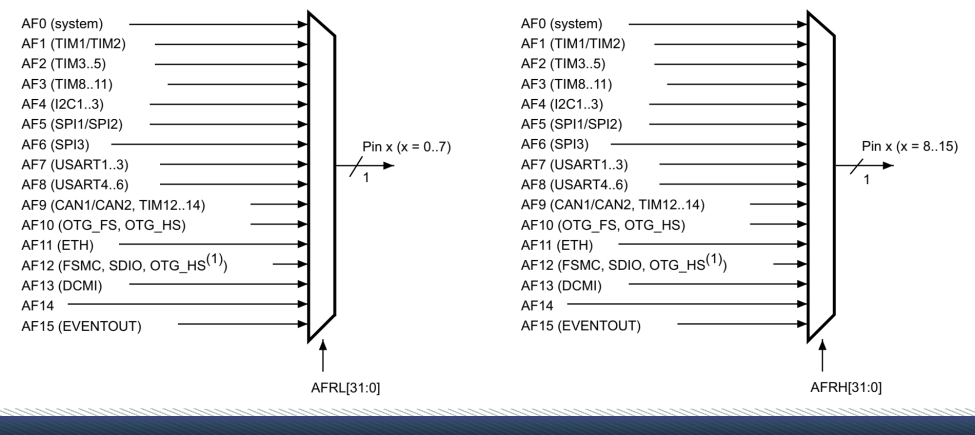

وقتی یک پایۀ GPIO در STM32 در مد AF پیکربندی می شود، توسط یک مالتی پلکسر، به واحدهای داخلی متصل می شود. مالتی پلکسر مذکور می تواند پایۀ GPIO را در 16 حالت به واحدهای داخلی مختلف وصل کند. مالتی پلکسر اجازه می دهد که هر پایه در یک زمان، تنها به یک واحد داخلی وصل باشد. رجیسترهای AFRH و AFRL تعیین می کنند که مالتی پلکسر، پایۀ GPIO را به کدام واحد داخلی متصل کند. در سری STM32F101/2/3/5/7xx مالتی پلکسر وجود ندارد و هر پایه می تواند به تعداد محدودی واحد داخلی متصل شود. در STM32F101/2/3/5/7xx، این عملکرد با Remap کردن امکان پذیر است و توسط رجیسترهای AFIO انجام می شود. در تصویر زیر شمایی از مالتی پلکسر نامبرده را برای سری STM32F205/07/15/17xx می بینیم.

تصویر 15 – انتخاب کنندۀ عملکردهای دیگر (Alternate function) پایه های GPIO در STM32F205/07/15/17xx

در دیتاشیت میکروکنترلرهای STM32 (به جز سری STM32F101/2/3/5/7xx) جداولی با عنوان Alternate function mapping وجود دارد. در این جداول عملکرد هر پایه از AF0 تا AF15 لیست شده است. جدول زیر لیست عملکردهای صفرم تا چهارم پایه های PA0 تا PA3 را نشان می دهد.

| AF4 | AF3 | AF2 | AF1 | AF0 | Port |

| I2C1/I2C2/I2C3 | TIM8/9/10/11 | TIM3/4/5 | TIM1/2 | SYS | |

| – | TIM8 ETR | TIM 5 CH1 | TIM2 CH1 ETR | – | PA0-WKUP |

| – | – | TIM5 CH2 | TIM2 CH2 | – | PA1 |

| – | TIM9 CH1 | TIM5 CH3 | TIM2 CH3 | – | PA2 |

| – | TIM9 CH2 | TIM5 CH4 | TIM2 CH4 | – | PA3 |

جدول 8 – عملکردهای صفرم تا چهارم پایه های PA0 تا PA3

نکته: عملکردهای آنالوگ مربوط به واحدهای ADC و DAC و …، در مدهای Alternate function قرار نگرفته اند و توسط بیت های رجیستر MODER انتخاب می شوند.

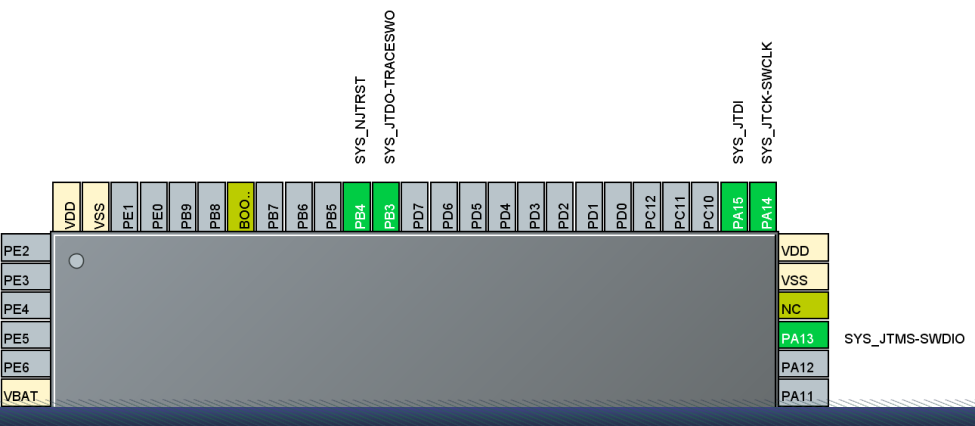

نکته: برای پروگرام کردن STM32 با روش های JTAG و SWD، پایه های مربوط به این دو ارتباط باید در مد AF و در حالت System یعنی AF0 قرار گیرند. در سری STM32F101/2/3/5/7xx، باید بیت های SWJ CFG در رجیستر MAPR مقداردهی شوند.

تصویر 16 – پایه های مربوط به JTAG و SWD در میکروکنترلر STM32F103VE

رجیسترهای GPIO در STM32

در این بخش به رجیسترهای واحد GPIO و همچنین رجیسترهای دیگر مربوط به راه اندازی GPIO در STM32 می پردازیم. سری STM32MP157 چند رجیستر اضافی و همچنین سری STM32F101/2/3/5/7xx دو رجیستر متفاوت دارد که در ادامه به صورت جداگانه بررسی خواهند شد.

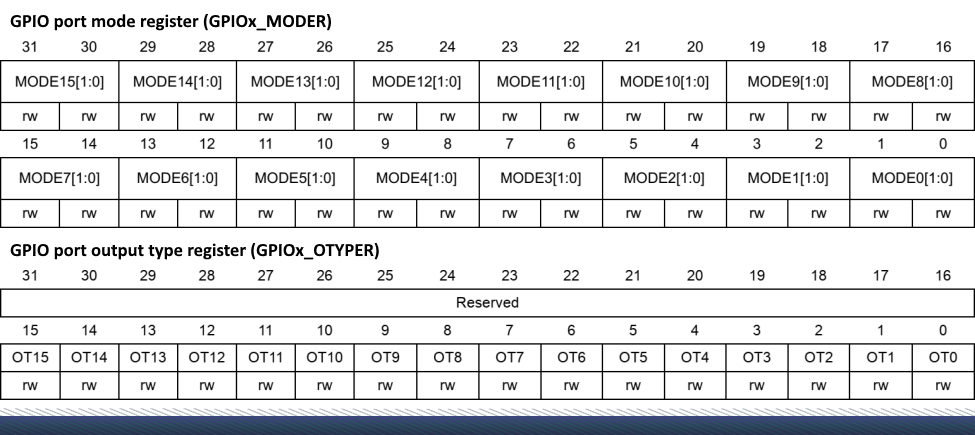

رجیستر MODER: بیت های این رجیستر مد پایه را تعیین می کنند:

MODEy[1:0] = (y=0..15)

- p00: Input

- p01: General purpose output

- p10: Alternate function

- p11: Analog

مد پیش فرض در سری های STM32L4+ و STM32H742/43/53xx و STM32H750xB و STM32WB55/35xx و STM32MP157 و STM32G0x1، آنالوگ است. در باقی سری ها مد پیش فرض Input است.

نکته: مقدار پیش فرض رجیستر MODER در سری های مختلف متفاوت است. در برخی سری ها مقادیر پیش فرض برای پورت های مختلف هم تفاوت دارد. برای مطالعۀ دقیق تر رجیسترها به Reference Manual میکروکنترلر مراجعه نمایید.

رجیستر OTYPER: بیت های این رجیستر نوع خروجی را تعیین می کند. اگر بیت OTy صفر باشد، خروجی پوش پول است. اگر یک باشد، خروجی Open-drain است. نوع پیش فرض برای همۀ سری ها، پوش پول است.

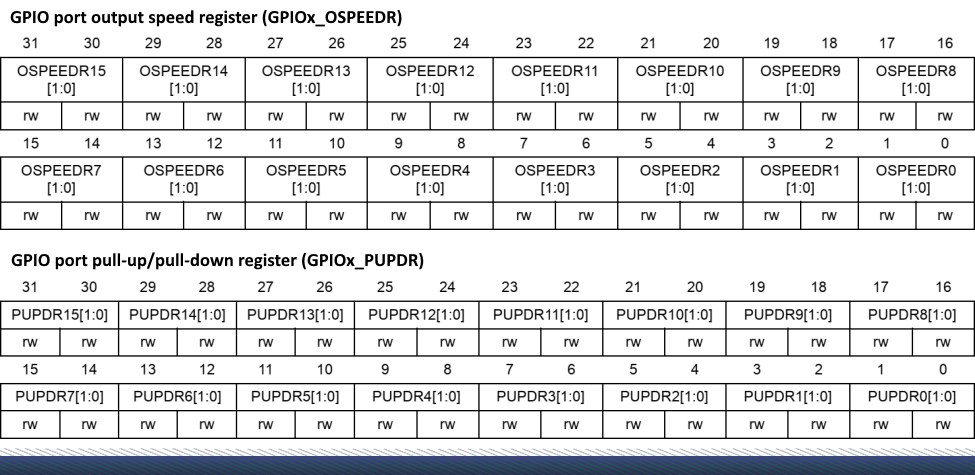

تصویر 17 – رجیسترهای MODER و OTYPER

رجیستر OSPEEDR: این رجیستر سرعت پایه های خروجی را تعیین می کند. در سری های مختلف عبارات مختلفی برای سرعت پایه های خروجی تعریف شده است. برای کسب اطلاعات دقیق دربارۀ سرعت پایه های خروجی در شرایط مختلف، به Reference Manual و دیتاشیت مراجعه نمایید. عبارات بیان کنندۀ سرعت پایه های خروجی در سری های مختلف به صورت زیر است:

OSPEEDRy[1:0] = (y=0..15)

- p00: Very low/Low speed

- p01: Low/Medium speed

- p10: Low/Fast/High speed

- p11: High/Very high speed

رجیستر PUPDR: این رجیستر تعیین کنندۀ وجود یا عدم وجود مقاومت پول آپ یا پول دون GPIO در STM32 به صورت زیر است:

PUPDRy[1:0] = (y=0..15)

- p00: No pull-up, no pull-down

- p01: Pull-up

- p10: Pull-down

- p11: Reserved

نکته: مقدار پیش فرض PUPDR برای پورت های مختلف در سری های مختلف، متفاوت است.

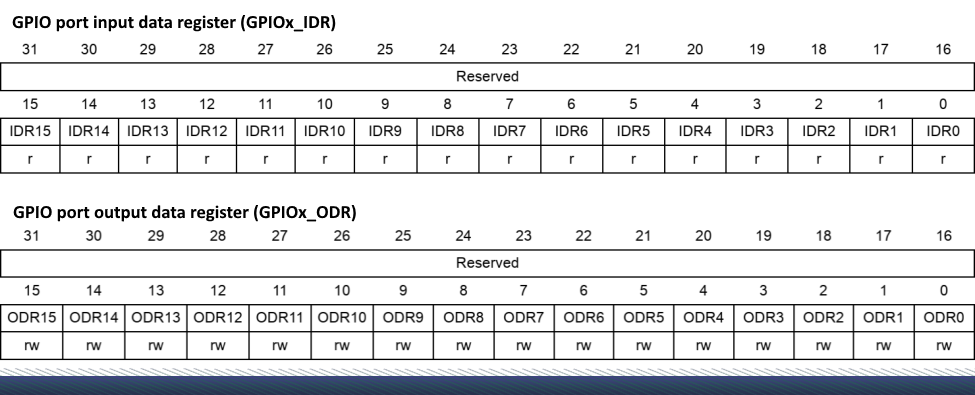

تصویر 18 – رجیسترهای OSPEEDR و PUPDR

رجیسترهای دادۀ ورودی/خروجی و BSRR و BRR

رجیسترهای دادۀ ورودی و خروجی GPIO در STM32، رجیسترهای IDR و ODR هستند. در مدهای Input و Output و AF، مقدار قرار گرفته روی پایه ها در رجیستر فقط خواندنی IDR ذخیره می شود. در مد آنالوگ، مقدار صفر در این رجیستر ذخیره می شود. در مد خروجی با خواندن رجیستر ODR، آخرین مقدار قرار گرفته روی پایۀ خروجی خوانده می شود. مقدار پیش فرض برای رجیستر IDR در همۀ سری ها نامشخص است. یعنی بیت های IDR پس از ریست، می توانند مقدار صفر یا یک را داشته باشند. مقدار پیش فرض برای بیت های رجیستر ODR نیز صفر است. همچنین در سری STM32WB55/35xx، بیت های ODR مربوط به پایه های PE5 تا PE15 و PH4 تا PH15 و PH2، رزرو هستند. رجیسترهای IDR و ODR در سری STM32F101/2/3/5/7xx نیز وجود دارند.

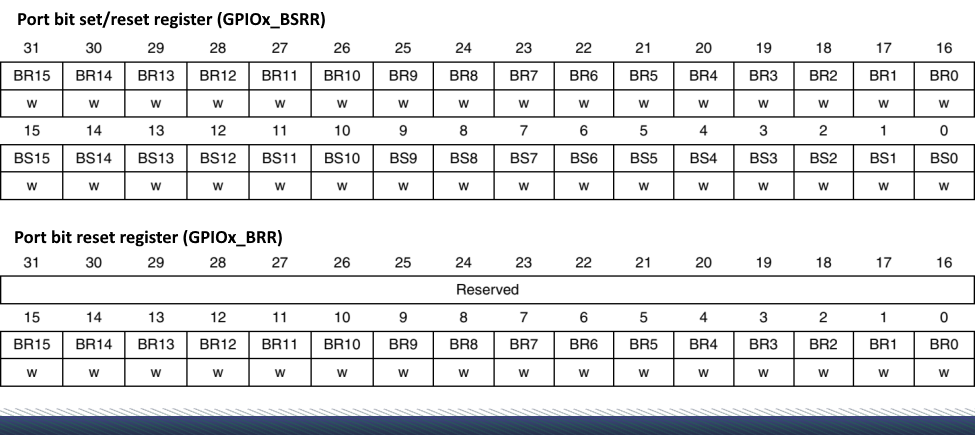

تصویر 19 – رجیسترهای IDR و ODR

برای مقداردهی بیتی به رجیستر ODR، رجیسترهای دیگری نیز وجود دارد. برای یک کردن بیت های ODR، می توان بیت های 0 تا 15 رجیستر BSRR را یک کرد. بیت های 0 تا 15 بیت های BSy هستند. برای صفر کردن بیت های ODR نیز می توان بیت های 16 تا 31 این رجیستر را یک کرد.بیت های 16 تا 31 بیت های BRy هستند. همچنین در برخی سری ها رجیستر BRR وجود دارد. برای صفر کردن بیت های ODR، می توان بیت های 0 تا 15 این رجیستر را یک کرد. رجیسترهای BSRR و BRR فقط نوشتنی هستند و نوشتن مقدار صفر در آنها بی معنی است. بنابراین برای این که تغییری در بیت های ODR ایجاد کنیم، باید در بیت متناظر در رجیستر صحیح، یک بنویسیم.

نکته: در رجیستر BSRR اگر بیت های BS و BR مربوط به یک پایه همزمان با هم یک شوند، اولویت با بیت BS است. یعنی این بیت عمل می کند و خروجی یک می شود.

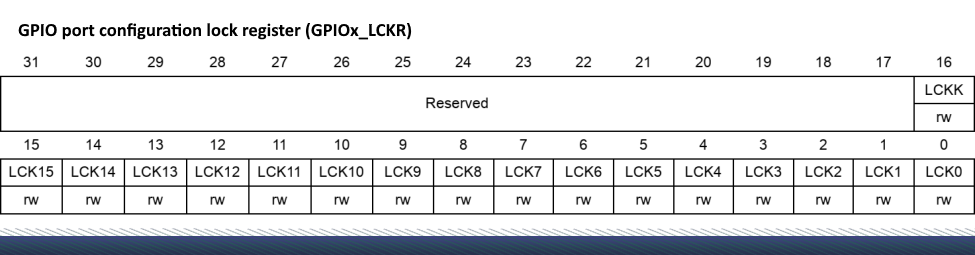

تصویر 20 – رجیسترهای BSRR و BRR

رجیسترهای تعیین عملکردهای دیگر GPIO در STM32

دو رجیستر برای تعیین عملکرد پایه در مد Alternate function وجود دارد. رجیستر AFRL عملکرد پایه های 0 تا 7 هر پورت را در مد AF انتخاب می کند. رجیستر AFRH نیز برای انتخاب عملکرد پایه های 8 تا 15 هر پورت در مد AF است. هر چهار بیت از این دو رجیستر به یک پایه اختصاص دارد. و مقداردهی به این بیت ها، عملکردهای AF0 تا AF15 را برای هر پایه انتخاب می کند. همان طور که قبلاً توضیح دادیم، در مد AF پایه ها توسط مالتی پلکسر به واحدهای داخلی متصل می شوند. مقدار 0 تا 15 به بیت های AFRLy[3:0] یا AFRHy[3:0]، عملکردهای AF0 تا AF15 را برای پایۀ Pxy میکروکنترلر تنظیم می کند. برای بررسی عملکردهای هر پایۀ GPIO در STM32، به جداول Alternate function mapping در دیتاشیت میکروکنترلر مراجعه نمایید. دقت شود که مقدار پیش فرض بیت های AFRL و AFRH در همۀ سری ها صفر است. همچنین در برخی سری ها، برخی مقادیر رزرو شده هستند. بنابراین بیت های AFRL و AFRH نمی توانند آن مقادیر را به خود بگیرند. به این نکته توجه شود که برای استفاده از مدهای AF، ابتدا رجیسترهای MODER و OTYPER و OSPEEDR و PUPDR مقداردهی شوند و سپس AFRH و AFRL.

AFRLy[3:0] or AFRHy[3:0] = (y=0..15)

- p0000: AF0

- p0001: AF1

- p0010: AF2

- p…

- p1111: AF15

تصویر 21 – رجیسترهای AFRH و AFRL

رجیستر قفل کردن پیکربندی GPIO در STM32

رجیستر LCKR این امکان را فراهم می کند که بتوان پیکربندی هر پایه را قفل کرد. این کار با فریز کردن بیت های مربوط در رجیسترهای MODER و OTYPER و OSPEEDR و PUPDR، انجام می شود. بیت های فریز شده، تا ریست بعدی میکروکنترلر یا پورت ورودی/خروجی مورد نظر، قابل تغییر نخواهند بود. بیت های 0 تا 15 این رجیستر مربوط به پایه های 0 تا 15 هر پورت هستند. یک کردن این بیت ها باعث فریز شدن پیکربندی پایۀ متناظر در پورت می شود. بیت 16 این رجیستر که LCKK نام دارد، نشان دهندۀ فعال یا غیر فعال بودن قفل پیکربندی است. هرگاه این بیت یک باشد، قفل پیکربندی فعال و هرگاه صفر باشد، قفل پیکربندی غیر فعال است. تغییر بیت های این رجیستر باید مطابق مراحل خاصی طی شود. این مراحل به ترتیب عبارتند از:

- ابتدا باید در بیت های 0 تا 15 نوشت و به همراه آن، بیت 16 را یک کرد.

- سپس باید همان مقدار قبلی را در بیت های 0 تا 15 نوشت و همزمان بیت 16 را صفر کرد.

- بعد از آن باید همان مقدار قبلی را در بیت های 0 تا 15 نوشت و همزمان بیت 16 را یک کرد.

- در این مرحله باید یک بار رجیستر LCKR خوانده شود.

- در نهایت باید یک بار دیگر رجیستر LCKR را خواند و از یک شدن بیت 16 اطمینان حاصل کرد.

دقت شود که حین نوشتن در رجیستر LCKR، مقدار بیت های 0 تا 15 نباید تغییر کند. همچنین باید توجه داشت که نوشتن در این رجیستر تنها به صورت 32 بیتی مجاز است. هر خطایی حین نوشتن در این رجیستر، باعث بی نتیجه شدن عملیات قفل کردن می شود.

نکته: پس از اولین عملیات موفق قفل کردن پیکربندی، LCKK یک می شود.

تصویر 22 – رجیستر LCKR

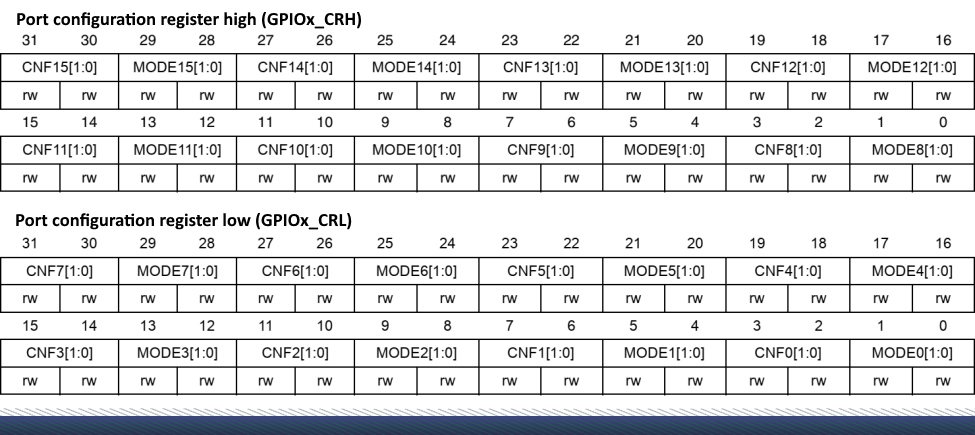

رجیسترهای GPIO در STM32 سری STM32F101/2/3/5/7xx

در سری STM32F101/2/3/5/7xx تنها رجیسترهای IDR و ODR و BSRR و BRR و LCKR همانند سری های قبل است. در این سری برای پیکربندی مدهای GPIO، از دو رجیستر CRL و CRH استفاده می شود. رجیستر CRL شامل بیت های CNF و MODE مربوط به پایه های 0 تا 7 هر پورت است. رجیستر CRH نیز شامل همان بیت ها برای پایه های 8 تا 15 پورت است. مقدار پیش فرض برای این دو رجیستر p0x44444444 است. بنابراین مد پیش فرض هر پایه Floating input است. در صورتی که بیت های MODE[1:0] برابر 00 باشند، بیت های CNF به صورت زیر هستند:

CNFy[1:0] = (y=0..7 in CRL, y=8..15 in CRH)

- p00: Analog mode

- p01: Floating input

- p10: Input with pull-up/pull-down

- p11: Reserved

در صورتی که بیت های MODE[1:0] برابر 01 یا 10 یا 11 باشند، بیت های CNF به شکل زیر هستند:

CNFy[1:0] = (y=0..7 in CRL, y=8..15 in CRH)

- p00: General purpose output push-pull

- p01: General purpose output Open-drain

- p10: Alternate function output Push-pull

- p11: Alternate function output Open-drain

بیت های MODE نیز خود به صورت زیر، تعیین کنندۀ مد یا سرعت پایۀ خروجی هستند:

MODEy[1:0] = (y=0..7 in CRL, y=8..15 in CRH)

- p00: Input mode

- p01: Output mode, max speed 10 MHz

- p10: Output mode, max speed 2 MHz

- p11: Output mode, max speed 50 MHz

تصویر 23 – رجیسترهای CRH و CRL

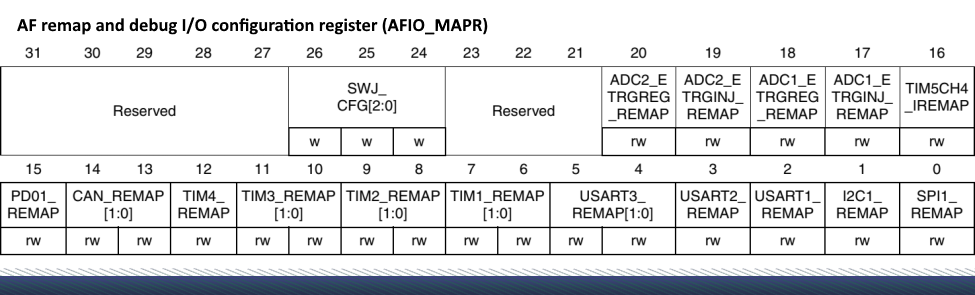

رجیسترهای AFIO در STM32F101/2/3/5/7xx

در سری STM32F101/2/3/5/7xx در مد Alternate function امکان اتصال پایه ها به تعداد محدودی واحد داخلی امکان پذیر است. این کار با رجیسترهای AFIO با عملکرد Remap انجام می شود. برخی واحدهای داخلی برای عملکردهای خود می توانند چند پایه از GPIO را به کار بگیرند. مثلاً در سری STM32F101/2/3/5/7xx، پایه های SCL و SDA واحد I2C1، به طور پیش فرض روی PB6 و PB7 هستند. این پایه ها با Remap کردن می توانند به پایه های PB8 و PB9 منتقل شوند. Remap در واقع به معنی جابه جا کردن عملکرد ورودی/خروجی یک واحد داخلی از پایه ای به پایۀ دیگر است. در سری های قبل که بررسی کردیم، عملیاتی مشابه Remap با کارکرد مجموع مالتی پلکسرهای پایه ها تحقق می یافت. در سری STM32F101/2/3/5/7xx مالتی پلکسری وجود ندارد و تنها چند رجیستر برای Remap کردن وجود دارد. رجیستر MAPR برای Remap پایه های بسیاری از واحدهای داخلی است. همان طور که در تصویر زیر می بینید، بیت 1 مربوط به I2C1 است. در صورتی که آن را صفر کنیم، SCL و SDA روی PB6 و PB7 هستند. در غیر این صورت SCL و SDA روی PB8 و PB9 هستند. بیت های دیگر نیز برای واحدهای داخلی دیگر به کار می روند. بیت های 24 تا 26 نیز که قبلاً توضیح دادیم، برای فعال و غیر فعال کردن JTAG و SWD هستند. برای مطالعۀ رجیسترهای AFIO و مشاهدۀ جداول مربوط به Remap واحدهای داخلی، به Reference Manual، بخش AFIO مراجعه نمایید. در ادامه به رجیسترهای دیگر مربوط به GPIO در STM32 می پردازیم.

تصویر 24 – رجیستر MAPR

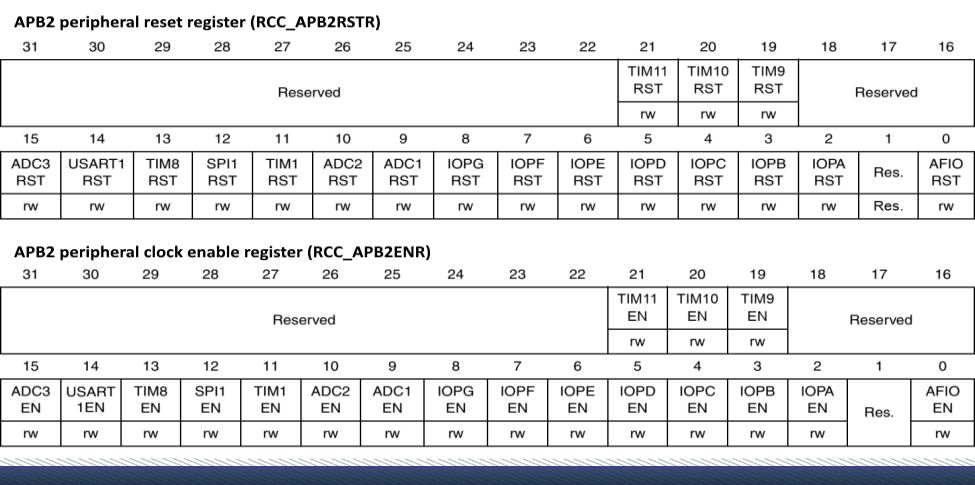

رجیسترهای مربوط به GPIO در STM32

پیش از راه اندازی GPIO در STM32 لازم است ابتدا در واحد RCC، رجیسترهایی را مقداردهی کنیم. در برخی سری ها GPIO روی باس AHB1 است. در برخی دیگر GPIO روی باس AHB4، در برخی روی APB2 و … است. ابتدا باید بدانیم که GPIO روی کدام باس قرار گرفته است. برای این کار باید به بخش Memory and bus architecture یا System and memory overview در Reference manual مراجعه کنیم. دو رجیستر RSTR و ENR به ترتیب برای ریست و فعال سازی کلاک واحدهای داخلی از جمله GPIO هستند. نام این رجیسترها با توجه به باس مورد نظر، معمولاً AHBxRSTR و AHBxENR یا APBxRSTR و APBxENR است. برای مثال در سری STM32F101/2/3/5/7xx، واحد GPIO روی APB2 است. در واحد RCC دو رجیستر APB2RSTR و APB2ENR وجود دارد. در APB2RSTR بیت هایی برای ریست و در APB2ENR بیت هایی برای فعال سازی کلاک پورت های ورودی/خروجی وجود دارد. در تصویر زیر این رجیسترها آورده شده اند. برای مطالعۀ رجیسترهای RCC مربوط به GPIO، به Reference manual مراجعه فرمایید.

نکته: نام رجیسترهای RCC مربوط به GPIO در برخی سری ها متفاوت است. مثلاً در سری STM32G0x1، نام این رجیسترها IOPRSTR و IOPENR است.

نکته: در سری STM32MP157 برای هر یک از عملکردهای ریست و فعال سازی GPIO یا واحدهای داخلی دیگر، دو رجیستر وجود دارد. یک رجیستر برای Set کردن و یک رجیستر برای Clear کردن.

نکته: پیش از تغییر بیت های رجیسترهای AFIO در STM32F101/2/3/5/7xx، باید بیت صفرم رجیستر APB2ENR را یک کرده باشیم.

نکته: در برخی سری ها رجیسترهای دیگری مربوط به GPIO وجود دارد. در سری هایی که I/O Compensation Cell دارند، در بخش SYSCFG رجیسترهایی برای فعال سازی و کنترل آن وجود دارد. همچنین سری STM32MP157 تعدادی رجیستر دیگر در بخش GPIO دارد که بررسی آنها فراتر از موضوع این نوشته است.

تصویر 25 – رجیسترهای APB2RSTR و APB2ENR

نتایج GPIO در STM32

- مفهوم GPIO در میکروکنترلرهای STM32، ورودی/خروجی ها با عملکرد پورت و عملکردهای مربوط به واحدهای داخلی دیگر است. مفهوم AFIO در STM32 نیز در میکروکنترلرهای STM32F101/2/3/5/7xx به معنی عملکردهای واحدهای داخلی روی پایه های ورودی/خروجی است. در STM32 واحد GPIO شامل پایه های I/O به همراه تمامی عملکردهای آنهاست. در سری STM32F101/2/3/5/7xx این واحد GPIO and AFIO نام دارد.

- بلوک دیاگرام GPIO در میکروکنترلرهای STM32 شامل بخش های اصلی دیودهای محافظ، مقاومت های پول آپ و پول دون، درایور ورودی و درایور خروجی است.

- مدهای GPIO در میکروکنترلرهای STM32 حاصل فعال یا غیر فعال بودن مقاومت های پول آپ و پول دون، نوع خروجی پوش پول یا Open-drain، فعال یا غیر فعال بودن ورودی/خروجی آنالوگ و استفاده یا عدم استفاده از عملکردهای دیگر (Alternate function) است.

- در پیکربندی مد Output در STM32، بافر خروجی (با آرایش پوش پول یا Open-drain) و ورودی اشمیت تریگر فعال هستند. در سری های به غیر از STM32F101/2/3/5/7xx مقاومت های پول آپ یا پول دون نیز می توانند فعال شوند.

- در پیکربندی مد Input در STM32، بافر خروجی غیر فعال است. همچنین ورودی اشمیت تریگر فعال است و مقاومت های پول آپ یا پول دون می توانند فعال شوند.

- در پیکربندی مد Alternate function در STM32، بافر خروجی (با آرایش پوش پول یا Open-drain) و ورودی اشمیت تریگر فعال هستند. همچنین مقاومت های پول آپ یا پول دون در سری های غیر از STM32F101/2/3/5/7xx، می توانند فعال شوند.

- در پیکربندی مد Analog در STM32، بافر خروجی و ورودی اشمیت تریگر و مقاومت های پول آپ و پول دون غیر فعال هستند. همچنین خروجی اشمیت تریگر در سطح صفر نگه داشته می شود.

- برای بررسی مشخصات الکتریکی و زمانی GPIO و پایه های هر پورت می توان به دیتاشیت مراجعه کرد.

- قفل GPIO در میکروکنترلرهای STM32، پیکربندی پایه های GPIO را تا ریست بعدی میکروکنترلر یا GPIOفریز می کند. عملیات فریز کردن شامل چند مرحله است که در صورت بروز خطا، بی نتیجه می ماند.

- می توان پایه های مربوط به کریستال خارجی اسیلاتورهای HSE و LSE را به عنوان GPIO استفاده کرد.

- مالتی پلکسر پایه های GPIO این امکان را فراهم می آورد که پایۀ پیکربندی شده در مد AF، بتواند به واحدهای داخلی متعدد وصل شود. پایۀ GPIO در یک زمان تنها می تواند یکی از عملکردهای AF0 تا AF15 را داشته باشد. در سری STM32F101/2/3/5/7xx مالتی پلکسر وجود ندارد.

- عملکردهای آنالوگ پایه های GPIO جدا از مدهای AF هستند.

- رجیسترهای MODER و OTYPER و OSPEEDR و PUPDR برای پیکربندی پایه های GPIO استفاده می شود. در سری STM32F101/2/3/5/7xx پیکربندی توسط رجیسترهای CRL و CRH و ODR انجام می شود.

- علاوه بر نوشتن مستقیم روی رجیستر ODR، می توان با رجیسترهای BSRR و BRR نیز روی آن نوشت.

- رجیسترهای AFRL و AFRH برای تعیین عملکردهای AF0 تا AF15 پایه ها است.

- در سری STM32F101/2/3/5/7xxاختصاص پایه ها به واحدهای داخلی به صورت محدود و با استفاده از Remap کردن است. Remap کردن در این سری توسط رجیسترهای AFIO انجام می شود. برای تغییر رجیسترهای AFIO باید ابتدا بیت صفرم رجیستر APB2ENR را یک کنیم.

- دو رجیستر مهم از واحد RCC برای راه اندازی و کار با GPIO وجود دارد. این دو رجیستر، رجیسترهای مربوط به ریست و فعال کردن کلاک پورت های I/O هستند.

نوشته های مرتبط در وبلاگ یوبرد:

آموزش های یوبرد مرتبط با این نوشته:

- فیلم آموزش GPIO در STM32

- فیلم آموزش ARM STM32 مقدماتی

- فیلم آموزش پورت IO در AVR

- فیلم آموزش میکروکنترلرهای AVR مقدماتی

- فیلم آموزش پورت IO در آردوینو

- فیلم آموزش آردوینو مقدماتی

مطالب کامل و عالی هستن. تشکر از یوبرد

خیلی لطف دارید. ممنون از مطالعه تون. خواهش میکنم