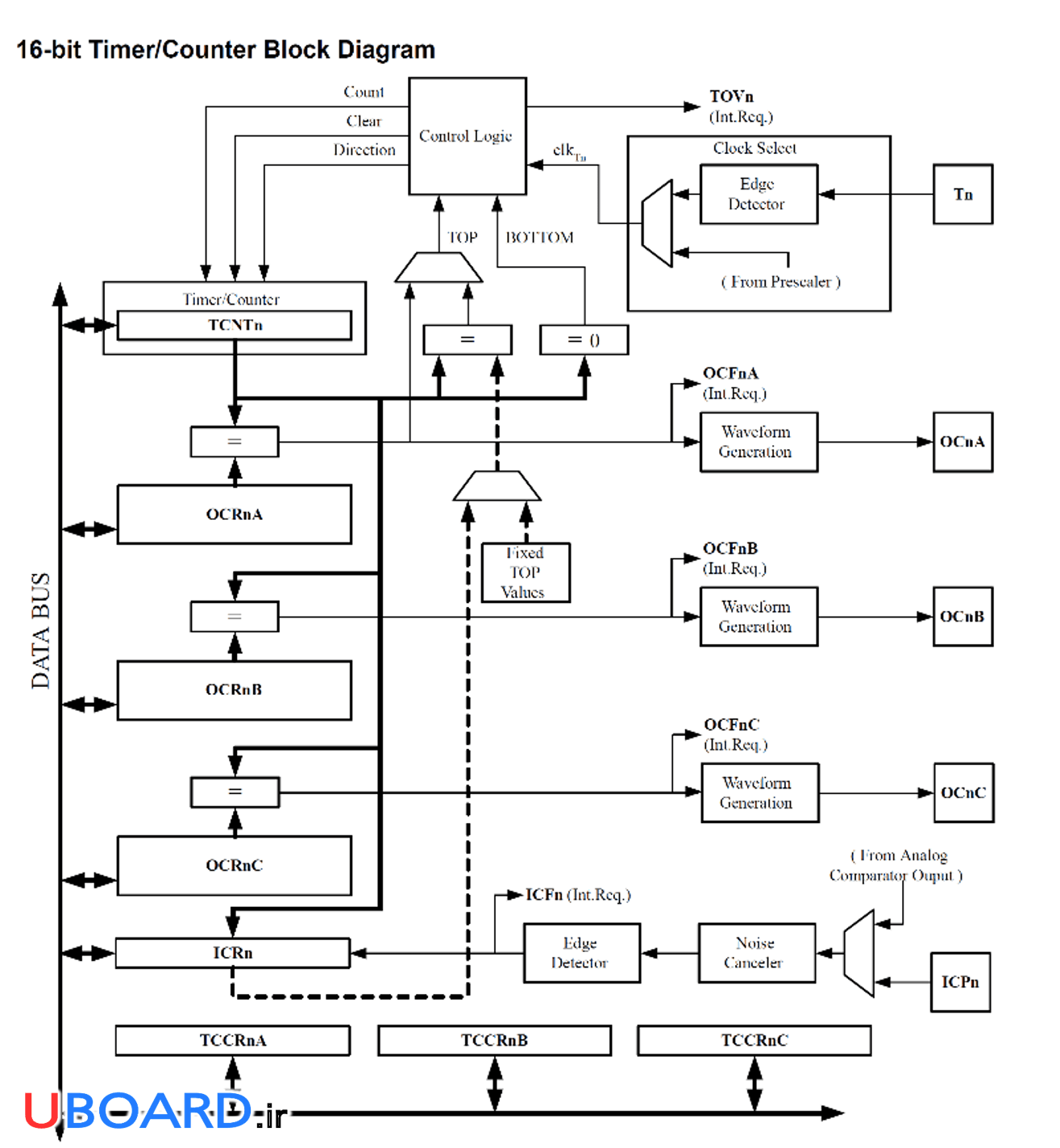

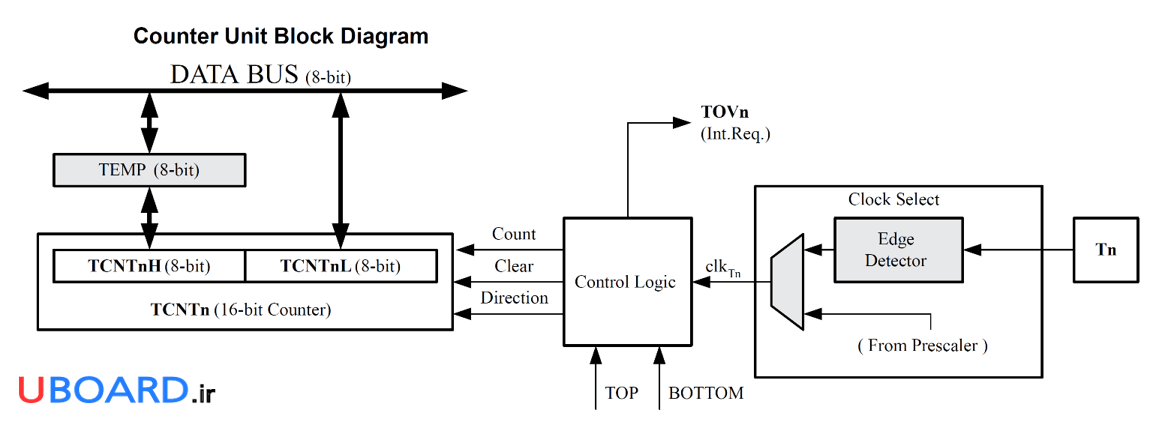

تایمر/کانتر 1 و 3 دقیقاً شبیه هم هستند. هر دو 16 بیتی هستند، هر کدام تعداد پنج وقفه، یک واحد Capture، سه واحد مقایسه، سه پایۀ خروجی برای تولید موج PWM، یک پایه برای کاربرد کانتر و یک پایه برای واحد Capture دارند.در این نوشته می خواهیم آموزش تایمر در AVR را با مبحث تایمر/کانتر 1 و 3 در ATmega128A به اتمام برسانیم. شکل زیر بلوک دیاگرام تایمر/کانتر 1 و 3 را نشان می دهد.

تصویر 1 – بلوک دیاگرام تایمر/کانتر 1 و 3 در میکروکنترلر ATmega128A

در پیکربندی ATmega103 Compatibility mode، تایمر/کانتر 3 در دسترس نیست و برای تایمر/کانتر 1 نیز رجیستر مقایسۀ A و B فعال هستند و رجیستر مقایسۀ C غیر فعال است.

فیلم آموزش تایمر در STM32 (فیلم آموزش ARM STM32 مقدماتی)

فیلم آموزش تایمر پیشرفته در STM32

فیلم آموزش تایمر در AVR (فیلم آموزش میکروکنترلرهای AVR مقدماتی)

فیلم آموزش تایمر پیشرفته در AVR

فیلم آموزش تایمر در آردوینو (فیلم آموزش آردوینو مقدماتی)

فیلم آموزش تایمر پیشرفته در آردوینو

چند اصطلاح در تایمر/کانتر 1 و 3

BOTTOM: کمترین مقدار تایمر/کانتر است. این مقدار برابر 0x0000 است.

MAX: بیشترین مقداری است که تایمر/کانتر می تواند به آن برسد. این مقدار برابر 0xFFFF (65535 دسیمال) است.

TOP: مقدار نهایی در مد مورد نظر است. TOP می تواند مقادیر ثابت 0x00FF، 0x01FF، 0x03FF یا مقادیر ذخیره شده در رجیسترهای OCRnA یا ICRn باشد. (n می تواند 1 یا 3 باشد.)

CM یا Compare Match: هر گاه مقدار تایمر/کانتر برابر رجیستر مقایسه شود به آن CM می گوییم.

حرف n: در بحث تایمر/کانتر 1 و 3 این حرف نشان دهندۀ شمارۀ تایمر/کانتر است. n می تواند 1 یا 3 باشد.

حرف x: در بحث تایمر/کانتر 1 و 3 این حرف نشان دهندۀ نام واحد مقایسه است. x می تواند A یا B یا C باشد.

حالت های خروجی مقایسه کننده های تایمر/کانتر 1 و 3

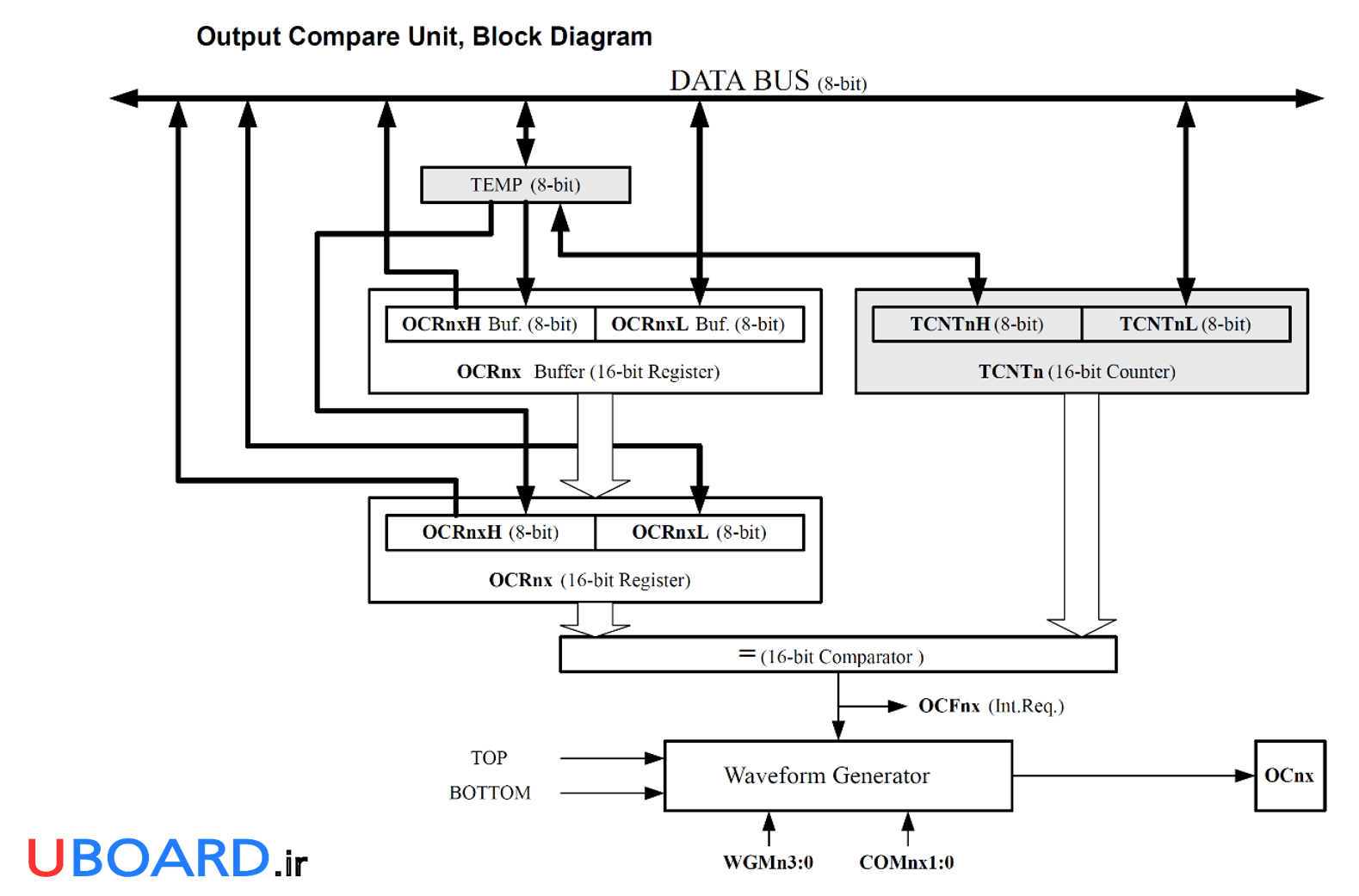

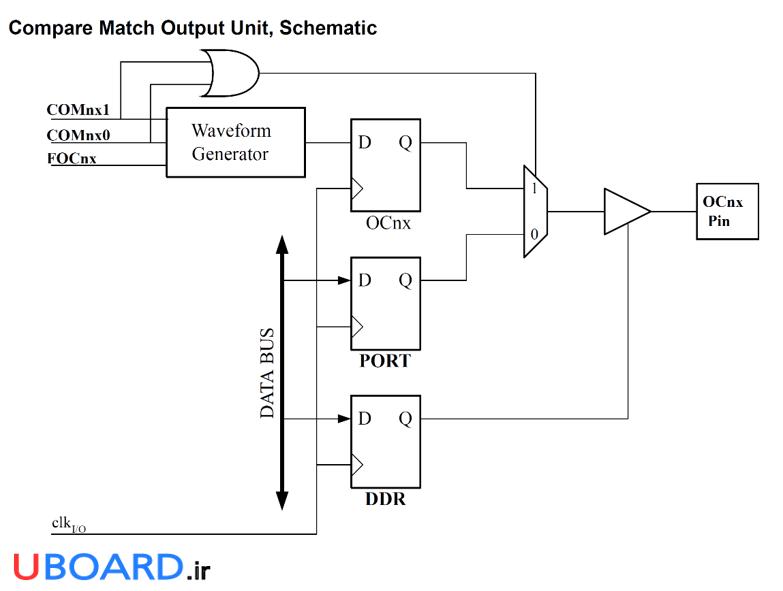

تصویر زیر نشان دهندۀ بلوک دیاگرام واحد مقایسۀ تایمر/کانتر 1 و 3 می باشد. هر کدام از واحد های مقایسه یک بخش Waveform generator دارند که شکل موج روی پایه های OCnx را می سازند. شکل موجی که روی این پایه ها ساخته می شود سه حالت دارند که در ادامه توضیح داده می شوند.

تصویر 2 – بلوک دیاگرام واحد مقایسۀ تایمر/کانتر 1 و 3 در میکروکنترلر ATmega128A

برای هر یک از خروجی های مقایسۀ A، B و C سه حالت وجود دارد. این حالت ها بیانگر نوعِ تغییر سطح ولتاژ روی پایه های مقایسه یعنی OCnA، OCnB و OCnC هستند. این حالت ها در هر کدام از مدهای تایمر/کانتر 1 و 3 متفاوت هستند. در جداول زیر به بررسی این حالت ها در مدهای مختلف می پردازیم. برای فهم آسان تر این حالت ها تصاویر مد ها را نیز مشاهده کنید.

حالت های OCnx در مد Normal و CTC – مدهای 0 و 4 و 12

تغییر وضعیت پایۀ OCnx در مدهای نرمال و CTC یعنی مدهای شمارۀ صفر، 4 و 12 به صورت زیر است.

| توضیحات | COMnx0 | COMnx1 |

| حالت disconnected

در این حالت خروجی های OCnx قطع هستند. |

0 | 0 |

| حالت Toggle

در این حالت هر گاه CM اتفاق بیفتد وضعیت پایۀ OCnx تغییر می کند. یعنی اگر 1 باشد 0 می شود و اگر 0 باشد 1 می شود. |

1 | 0 |

| حالت Clear OCnx on compare match

در این حالت وقتی CM اتفاق می افتد، پایۀ OCnx همواره صفر می باشد. |

0 | 1 |

| حالت Set OCnx on compare match

در این حالت وقتی CM اتفاق می افتد، پایۀ OCnx همواره یک می باشد. |

1 | 1 |

جدول 1 – حالت های OCnx در مد نرمال و CTC تایمر/کانتر 1 و 3

حالت های OCnx در مدهای PWM سریع (Fast PWM) – مدهای 5 و 6 و 7 و 14 و 15

در مدهای PWM سریع پایه های OCnx به صورت زیر تتغییر می کنند.

| توضیحات | COMnx0 | COMnx1 |

| حالت disconnected

در این حالت خروجی های OCnx قطع هستند. |

0 | 0 |

| حالت Toggle

– این حالت تنها در مد 15 وجود دارد و تنها برای خروجی OCnA. هر گاه CM اتفاق بیفتد خروجی OCnA تغییر وضعیت می دهد. یعنی toggle می شود. – پایه های OCnB و OCnC در این حالت قطع هستند. |

1 | 0 |

| حالت non-inverting (حالت PWM ناوارون)

– در این حالت هر گاه CM اتفاق بیفتد، پایۀ OCnx صفر می شود و هر گاه تایمر به BOTTOM برسد، پایۀ OCnx یک می شود.

– در مد 15 هنگام اتفاق افتادن CM، خروجی OCnA همواره یک می باشد.

– دلیل این که نام این حالت، PWM ناوارون است این است که با افزایش دادنِ مقدار رجیسترِ OCRnx عرض پالس های روی OCnx افزایش می یابد. یعنی Duty Cycle آنها زیاد می شود. |

0 | 1 |

| حالت inverting (حالت PWM وارون)

– در این حالت هر گاه CM اتفاق بیفتد، پایۀ OCnx یک می شود و هر گاه تایمر به BOTTOM برسد، پایۀ OCnx صفر می شود.

– در مد 15 هنگام اتفاق افتادن CM، خروجی OCnA همواره صفر می باشد.

– دلیل این که نام این حالت، PWM وارون است، این است که با افزایش دادنِ مقدار رجیسترِ OCRnx عرض پالس های روی OCnx کاهش می یابد. یعنی Duty Cycle آنها کم می شود. |

1 | 1 |

جدول 2 – حالت های OCnx در مد PWM سریع تایمر/کانتر 1 و 3

حالت های OCnx در مد PWM تصحیح فاز و PWM تصحیح فاز و فرکانس

در مدهای PWM تصحیح فاز (PWM,Phase Correct) و مدهای PWM تصحیح فاز و فرکانس (PWM,Phase and Frequency Correct) که همان مدهای شمارۀ 1 و 2 و 3 و 10 و 11 و 8 و 9 هستند، وضعیت پایه های OCnx به صورت زیر است.

| توضیحات | COMnx0 | COMnx1 |

| حالت disconnected

در این حالت خروجی های OCnx قطع هستند. |

0 | 0 |

| حالت Toggle

– این حالت تنها در مد 9 و 11 وجود دارد و تنها برای خروجی OCnA. هر گاه CM اتفاق بیفتد خروجی OCnA تغییر وضعیت می دهد. یعنی toggle می شود. همچنین پایه های OCnB و OCnC در این حالت قطع هستند. – در مد های 1، 2، 3، 8 و 10 هر سه خروجی OCnA، OCnB و OCnC قطع هستند. |

1 | 0 |

| حالت non-inverting (حالت PWM ناوارون)

– در این حالت هر گاه CM در شمارش صعودی اتفاق بیفتد، پایۀ OCnx صفر می شود و هر گاه CM در شمارش نزولی اتفاق بیفتد، پایۀ OCnx یک می شود.

– در مد 9 و 11 هنگام اتفاق افتادن CM خروجی OCnA همواره یک می باشد.

– دلیل این که نام این حالت، PWM ناوارون است این است که با افزایش دادنِ مقدار رجیسترِ OCRnx عرض پالس های روی OCnx افزایش می یابد. یعنی Duty Cycle آنها زیاد می شود. |

0 | 1 |

| حالت inverting (حالت PWM وارون)

– در این حالت هر گاه CM در شمارش صعودی اتفاق بیفتد، پایۀ OCnx یک می شود و هر گاه CM در شمارش نزولی اتفاق بیفتد، پایۀ OCnx صفر می شود.

– در مد 9 و 11 هنگام اتفاق افتادن CM خروجی OCnA همواره صفر می باشد.

– دلیل این که نام این حالت، PWM وارون است، این است که با افزایش دادنِ مقدار رجیسترِ OCRnx عرض پالس های روی OCnx کاهش می یابد. یعنی Duty Cycle آنها کم می شود. |

1 | 1 |

جدول 3 – حالت های OCnx در مد PWM تصحیح فاز و PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3

مدهای عملیاتی تایمر/کانتر 1 و 3 در میکروکنترلر ATmega128A

تایمر/کانتر 1 و 3 می توانند 14 مد عملیاتی داشته باشند که آن ها را در جدول زیر مشاهده می کنید. در انتهای توضیحات هر مد یک تصویر حاوی نمودار تایمر/کانتر و شکل موج های خروجی آن با توجه به حالت های مختلف خروجی قرار گرفته است. توضیحات این جداول و تصاویر موجود در فایل های PDF مربوط به آنها بسیار مهم هستند.

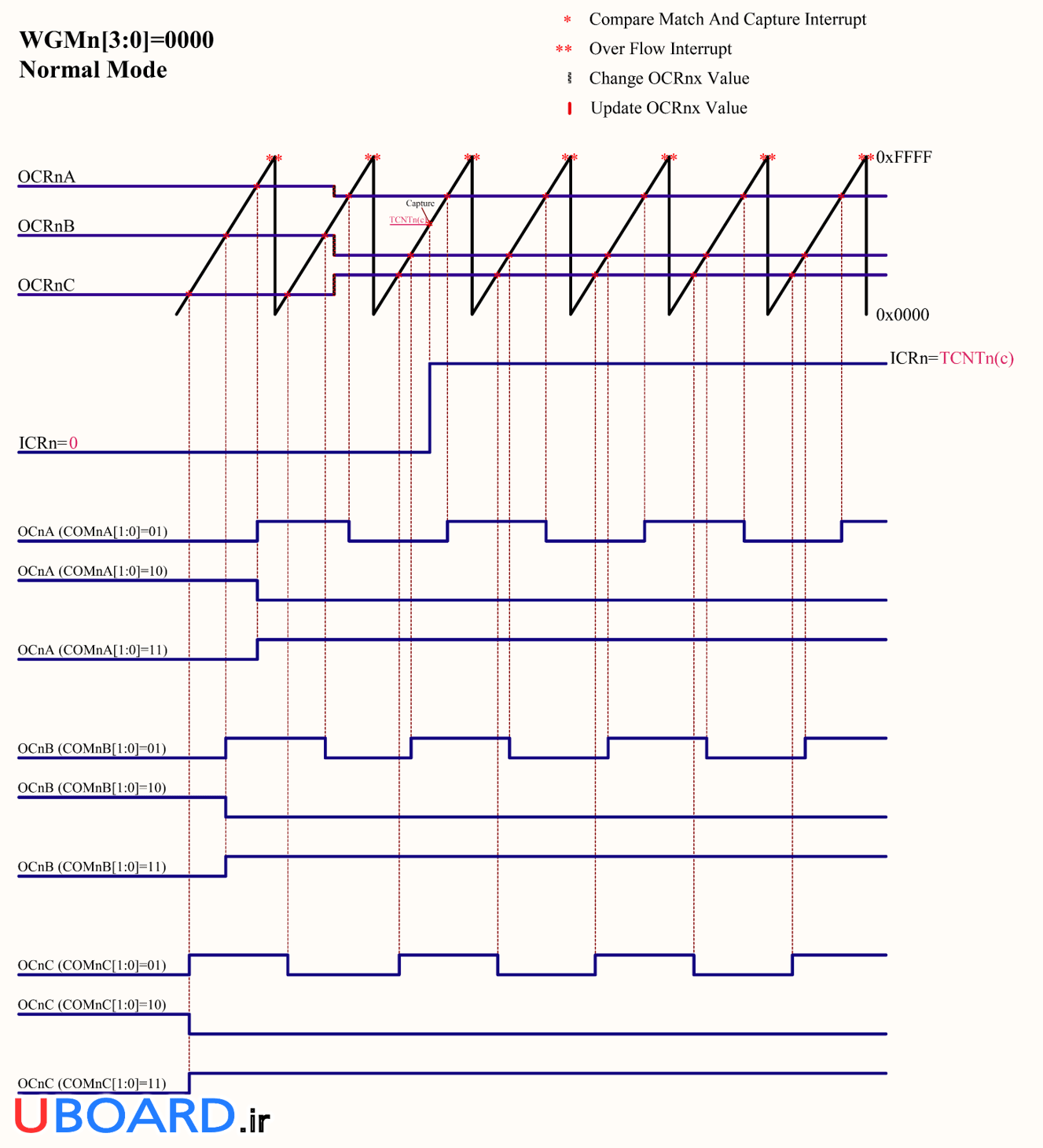

مد Normal تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ صفر)

مشخصات مد نرمال تایمر/کانتر 1 و 3 در ATmega128A به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| MAX | Immediate | 0xFFFF | Normal | 0 | 0 | 0 | 0 | 0 |

جدول 4 – مشخصات مد نرمال تایمر/کانتر 1 و 3

توضیحات مد نرمال تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر/کانتر تا مقدار MAX بالا می رود و پس از آن سرریز می شود و از مقدار BOTTOM شروع به شمارش می کند.

- هر جایی که رجیسترهای مقایسه مقدار دهی شوند، مقدار آنها فوراً در آن رجیسترها قرار می گیرد.

- در این مد سرریز در MAX اتفاق می افتد و هر گاه تایمر/کانتر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد.

- در این مد اگر واحد capture تحریک شود، مقدار تایمر/کانتر در رجیستر ICRn ذخیره می شود و وقفۀ capture در صورت فعال بودن اتفاق می افتد. (ابتدا وقفه اتفاق می افتد سپس مقدار تایمر/کانتر در رجیستر ICRn ذخیره می شود.)

تصویر 3 – نمودار زمانی مد نرمال تایمر/کانتر 1 و 3 و شکل موج روی OCnx

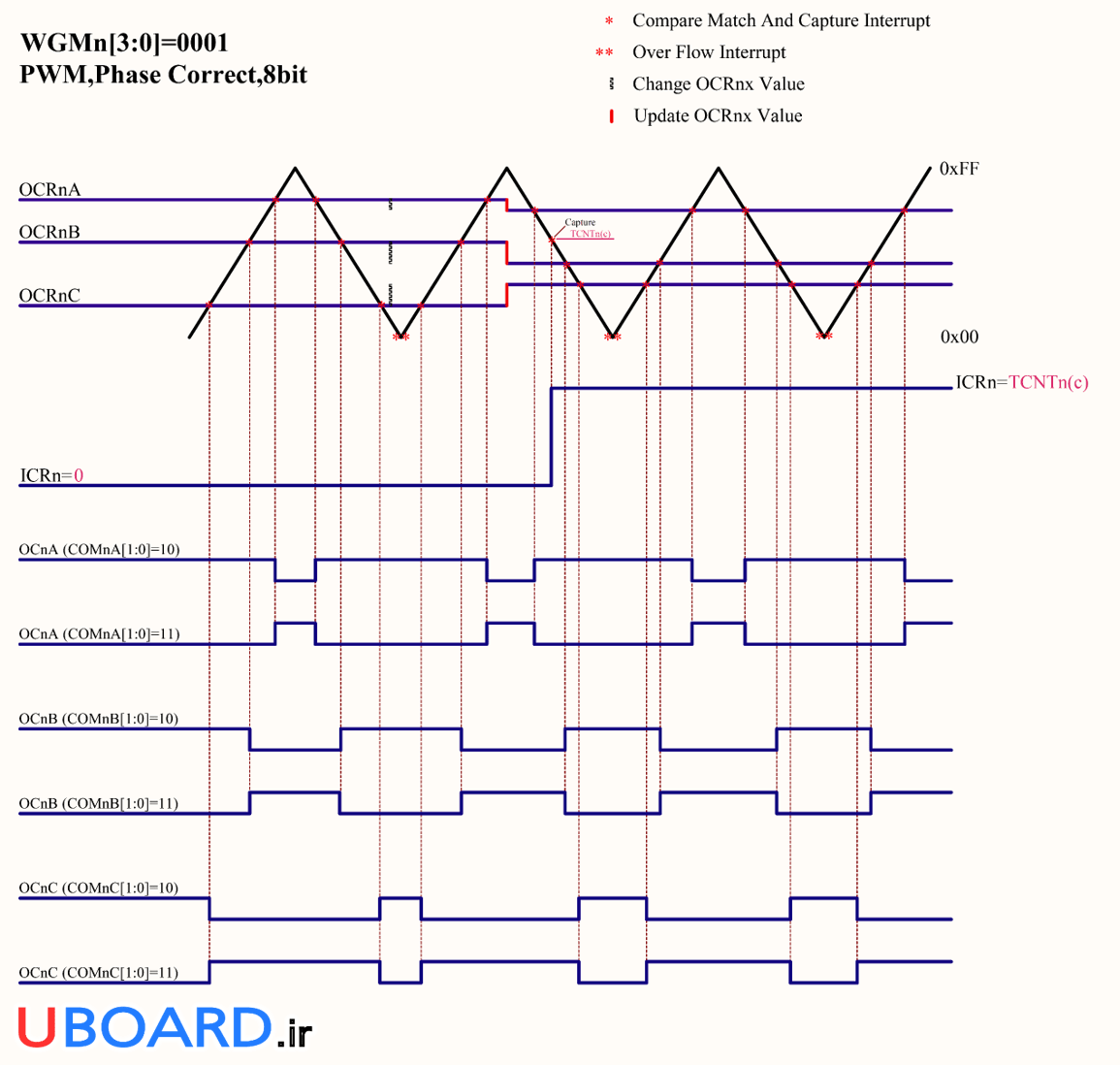

مد PWM تصحیح فاز 8 بیتی تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 1)

مشخصات مد PWM,Phase Correct,8bit تایمر/کانتر 1 و 3 به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| BOTTOM | TOP | 0x00FF | PWM,Phase Correct,8bit | 1 | 0 | 0 | 0 | 1 |

جدول 5 – مشخصات مد PWM تصحیح فاز 8 بیتی تایمر/کانتر 1 و 3

توضیحات مد PWM تصحیح فاز 8 بیتی در تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر تا مقدار 0x00FF بالا می رود و سپس به صورت نزولی تا مقدار BOTTOM می شمارد. و دوباره جهت شمارش صعودی می شود.

- در این مد هر جایی که رجیسترهای مقایسه مقدار دهی شوند مقدار آن ها در زمانی که تایمر به TOP می رسد، در آن رجیسترها قرار می گیرد.

- در این مد سرریز وقتی اتفاق می افتد که مقدار تایمر (در حالی که جهت شمارش نزولی دارد) به BOTTOM برسد. هرگاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد.

- در این مد اگر واحد capture تحریک شود، مقدار تایمر در رجیستر ICRn ذخیره می شود و وقفۀ capture در صورت فعال بودن اتفاق می افتد. (ابتدا وقفه اتفاق می افتد سپس مقدار تایمر در رجیستر ICRn ذخیره می شود.)

تصویر 4 – نمودار زمانی مد PWM تصحیح فاز 8 بیتی تایمر/کانتر 1 و 3 و شکل موج روی OCnx

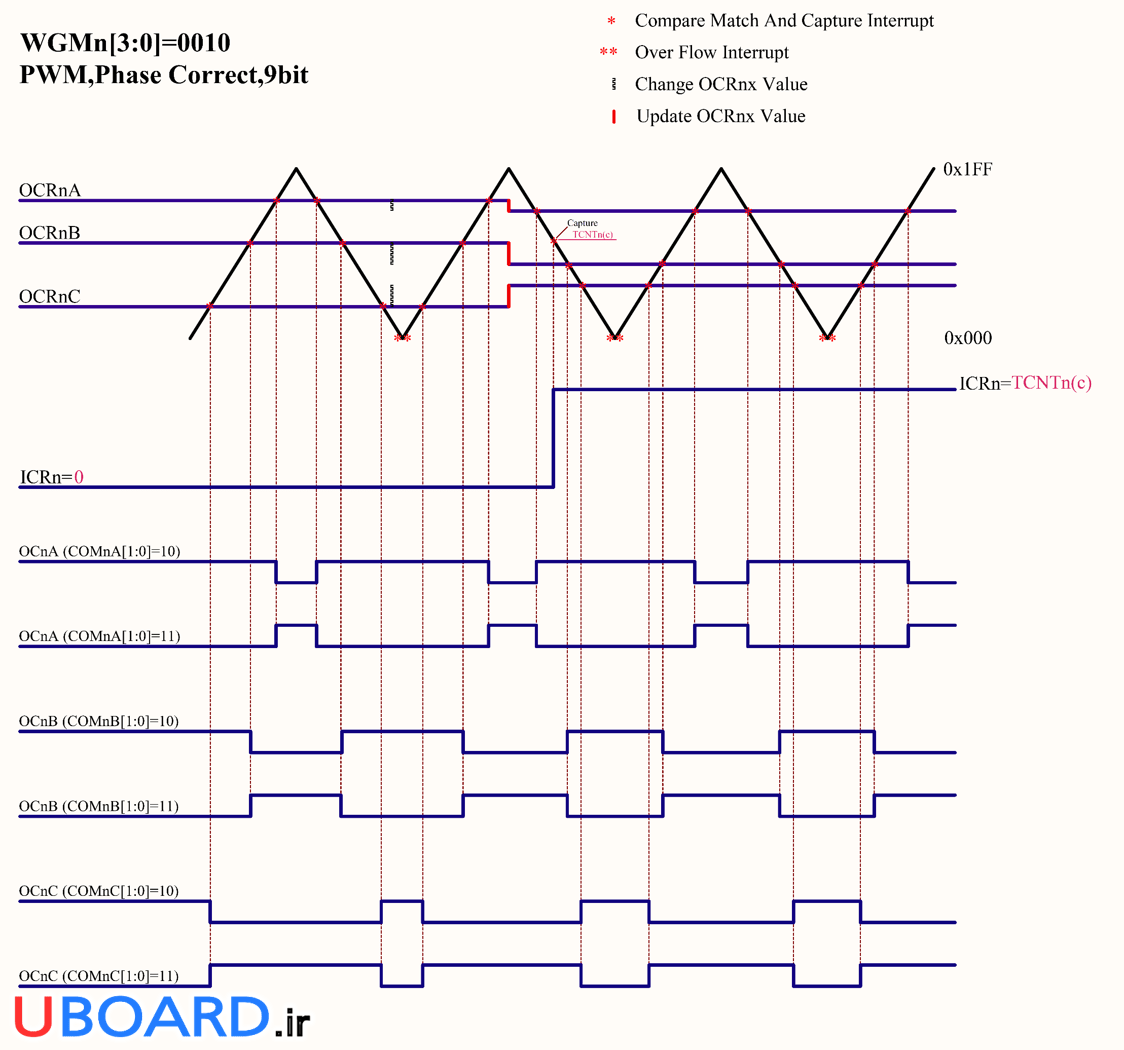

مد PWM تصحیح فاز 9 بیتی تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 2)

مشخصات مد PWM,Phase Correct,9bit در تایمر/کانتر 1 و 3 به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| BOTTOM | TOP | 0x01FF | PWM,Phase Correct,9bit | 0 | 1 | 0 | 0 | 2 |

جدول 6 – مشخصات مد PWM تصحیح فاز 9 بیتی تایمر/کانتر 1 و 3

عملکرد مد PWM تصحیح فاز 9 بیتی تایمر/کانتر 1 و 3 شبیه مد شمارۀ 1 است. تنها تفاوت آن مقدار TOP است. مقدار تایمر در این مد تا 0x01FF بالا می رود.

تصویر 5 – نمودار زمانی مد PWM تصحیح فاز 9 بیتی تایمر/کانتر 1 و 3 و شکل موج روی OCnx

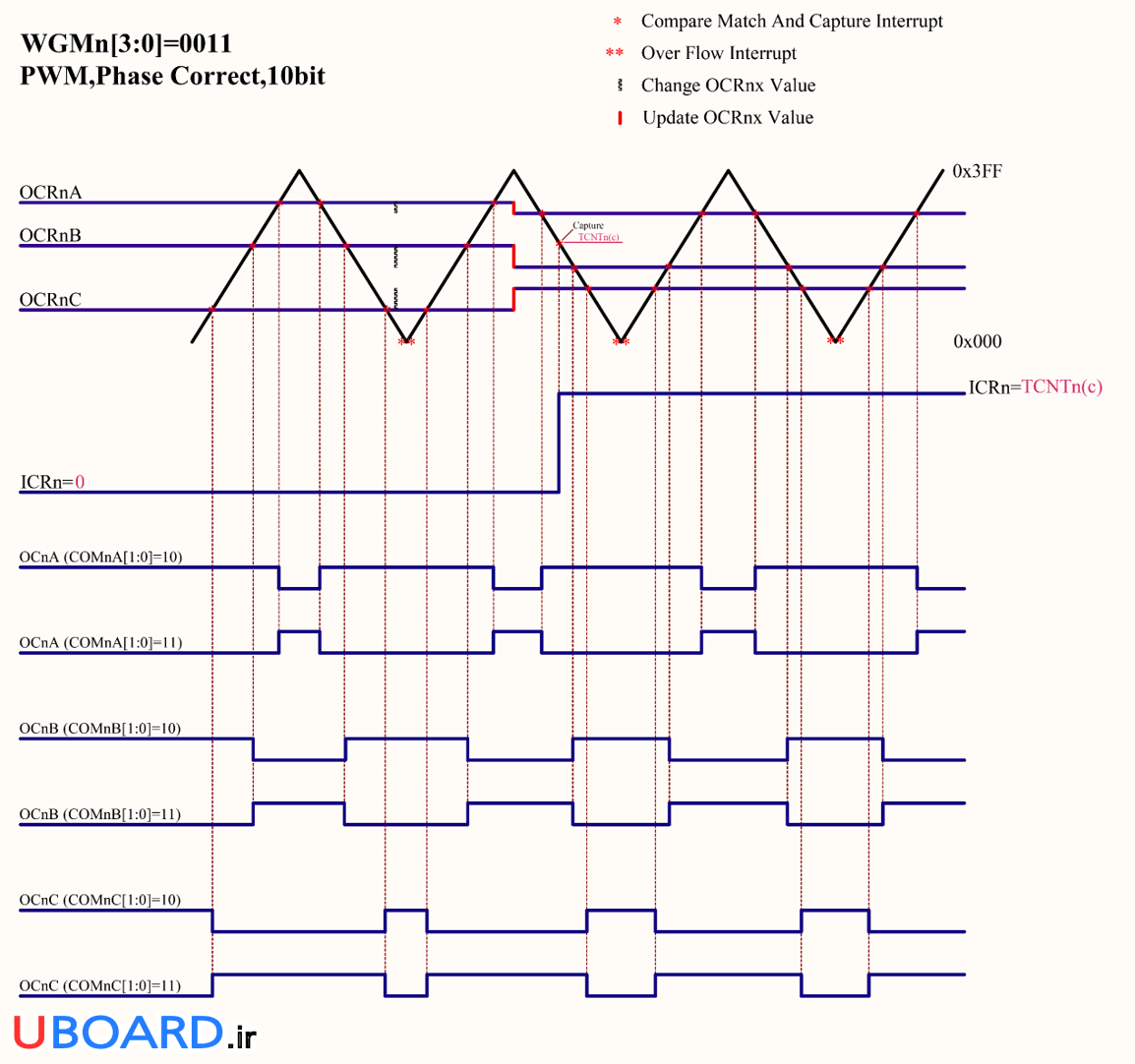

مد PWM تصحیح فاز 10 بیتی تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 3)

مشخصات مد PWM,Phase Correct,10bit تایمر/کانتر 1 و 3 به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| BOTTOM | TOP | 0x03FF | PWM,Phase Correct,10bit | 1 | 1 | 0 | 0 | 3 |

جدول 7 – مشخصات مد PWM تصحیح فاز 10 بیتی تایمر/کانتر 1 و 3

عملکرد مد PWM تصحیح فاز 10 بیتی شبیه مد شمارۀ 1 است. تنها تفاوت آن مقدار TOP است. مقدار تایمر در این مد تا 0x03FF بالا می رود.

تصویر 6 – نمودار زمانی مد PWM تصحیح فاز 10 بیتی تایمر/کانتر 1 و 3 و شکل موج روی OCnx

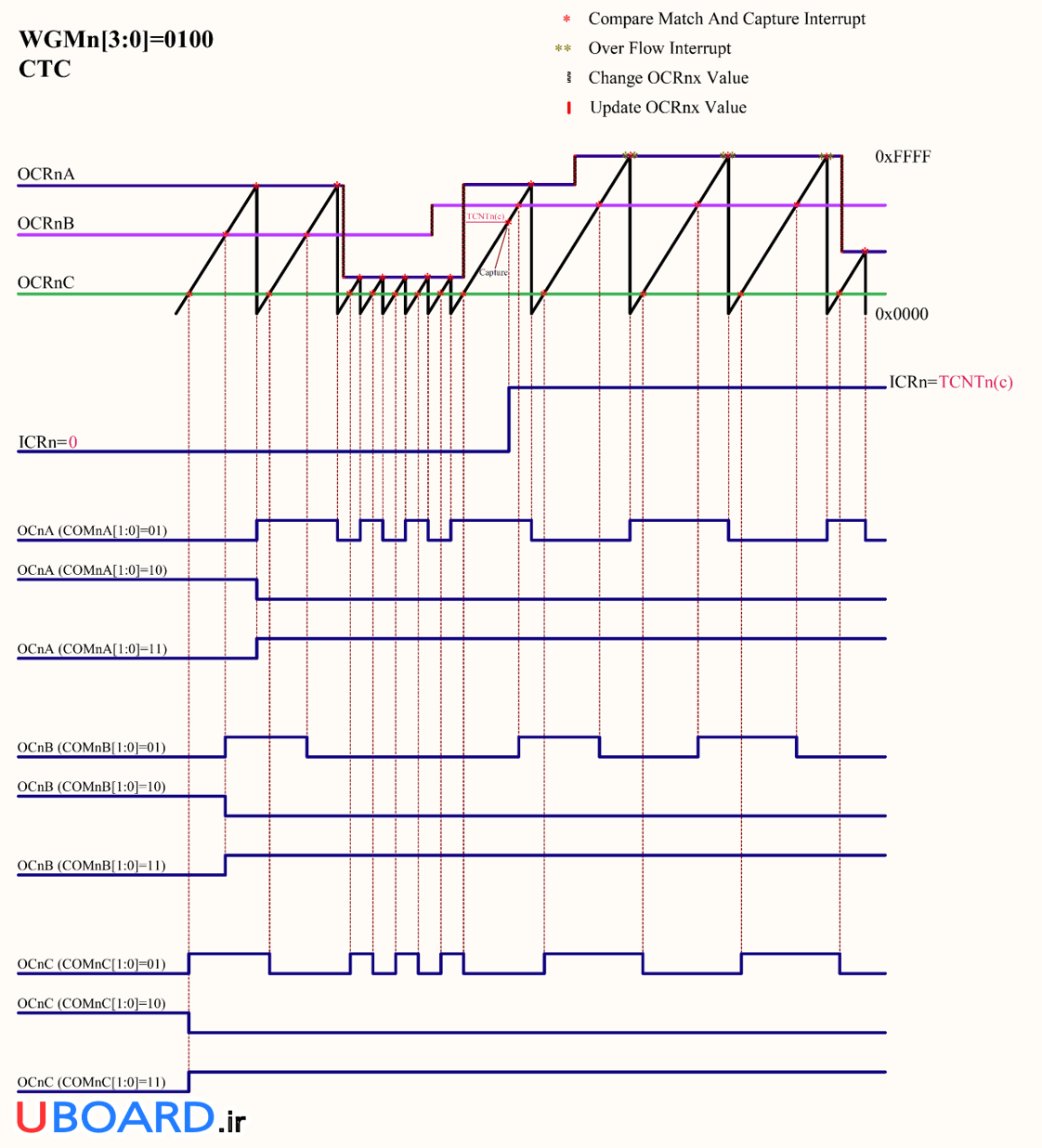

مد CTC تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 4)

مشخصات مد CTC تایمر/کانتر 1 و 3 در ATmega128A به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| MAX | Immediate | OCRnA | CTC | 0 | 0 | 1 | 0 | 4 |

جدول 8 – مشخصات مد CTC تایمر/کانتر 1 و 3 (مد شمارۀ 4)

توضیحات مد CTC (Clear Timer on Compare Match) تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر تا مقدار رجیستر OCRnA می شمارد و پس از آن به مقدار BOTTOM می رسد و دوباره از BOTTOM شروع به شمارش می کند.

- مقدار TOP را رجیستر OCRnA تعیین می کند. همچنین می توان OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM برای رجیسترهای مقایسۀ B و C اتفاق بیفتد، مقدار رجیسترهای OCRnB و OCRnC باید کمتر از OCRnA باشد.

- مقادیر جدید برای رجیسترهای مقایسه فوراً در آنها قرار می گیرد.

- سرریز در MAX اتفاق می افتد و این امر تنها زمانی امکان پذیر است که OCRnA=MAX (یعنی 0xFFFF) باشد. هر گاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد. وقفۀ مقایسۀ A نیز به هنگام رسیدن تایمر به OCRnA (TOP) اتفاق می افتد.

- در این مد اگر واحد capture تحریک شود، مقدار تایمر در رجیستر ICRn ذخیره می شود و وقفۀ capture در صورت فعال بودن اتفاق می افتد. (ابتدا وقفه اتفاق می افتد سپس مقدار تایمر در رجیستر ICRn ذخیره می شود.)

تصویر 7 – نمودار زمانی مد CTC تایمر/کانتر 1 و 3 (مد شمارۀ 4) و شکل موج روی OCnx

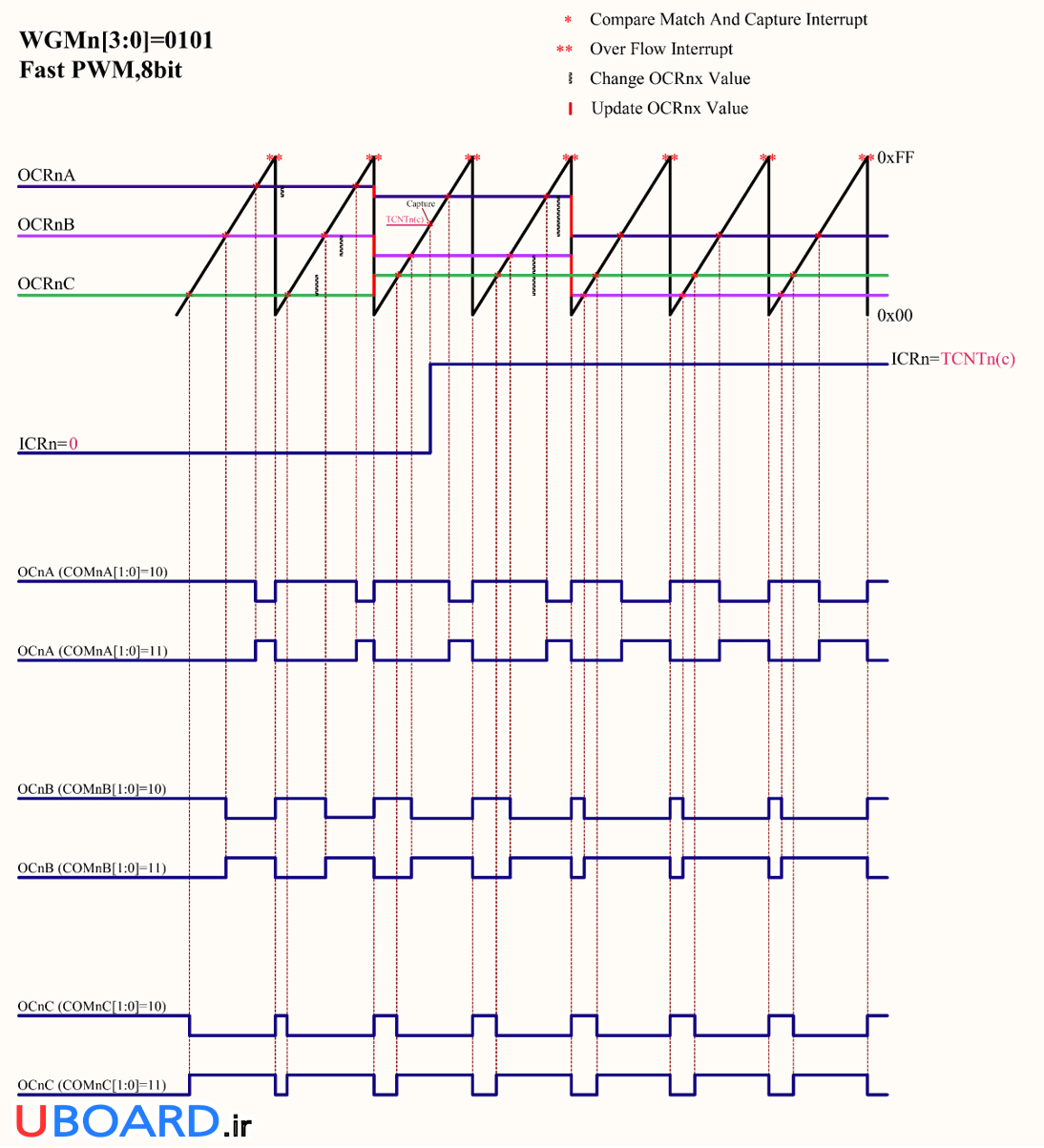

مد Fast PWM,8bit تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 5)

مشخصات مد PWM سریع 8 بیتی تایمر/کانتر 1 و 3 در ATmega128A را در جدول زیر مشاهده می کنید.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| TOP | BOTTOM | 0x00FF | Fast PWM,8bit | 1 | 0 | 1 | 0 | 5 |

جدول 9 – مشخصات PWM سریع 8 بیتی در تایمر/کانتر 1 و 3

توضیحات مد PWM سریع 8 بیتی (Fast PWM,8bit) تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر تا مقدار 0x00FF بالا می رود و پس از آن سرریز می شود و مقدارش به BOTTOM می رسد و دوباره از BOTTOM می شمارد.

- هر جایی که رجیسترهای مقایسه مقدار دهی شوند این مقدار در زمانی که تایمر به BOTTOM می رسد، در رجیسترهای مقایسه قرار داده می شوند.

- در این مد سرریز در مقدار TOP که برابر 0x00FF است اتفاق می افتد. هرگاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد.

- در این مد اگر واحد capture تحریک شود، مقدار تایمر در رجیستر ICRn ذخیره می شود و وقفۀ capture در صورت فعال بودن اتفاق می افتد. (ابتدا وقفه اتفاق می افتد سپس مقدار تایمر در رجیستر ICRn ذخیره می شود.)

تصویر 8 – نمودار زمانی مد PWM سریع 8 بیتی تایمر/کانتر 1 و 3 و شکل موج روی OCnx

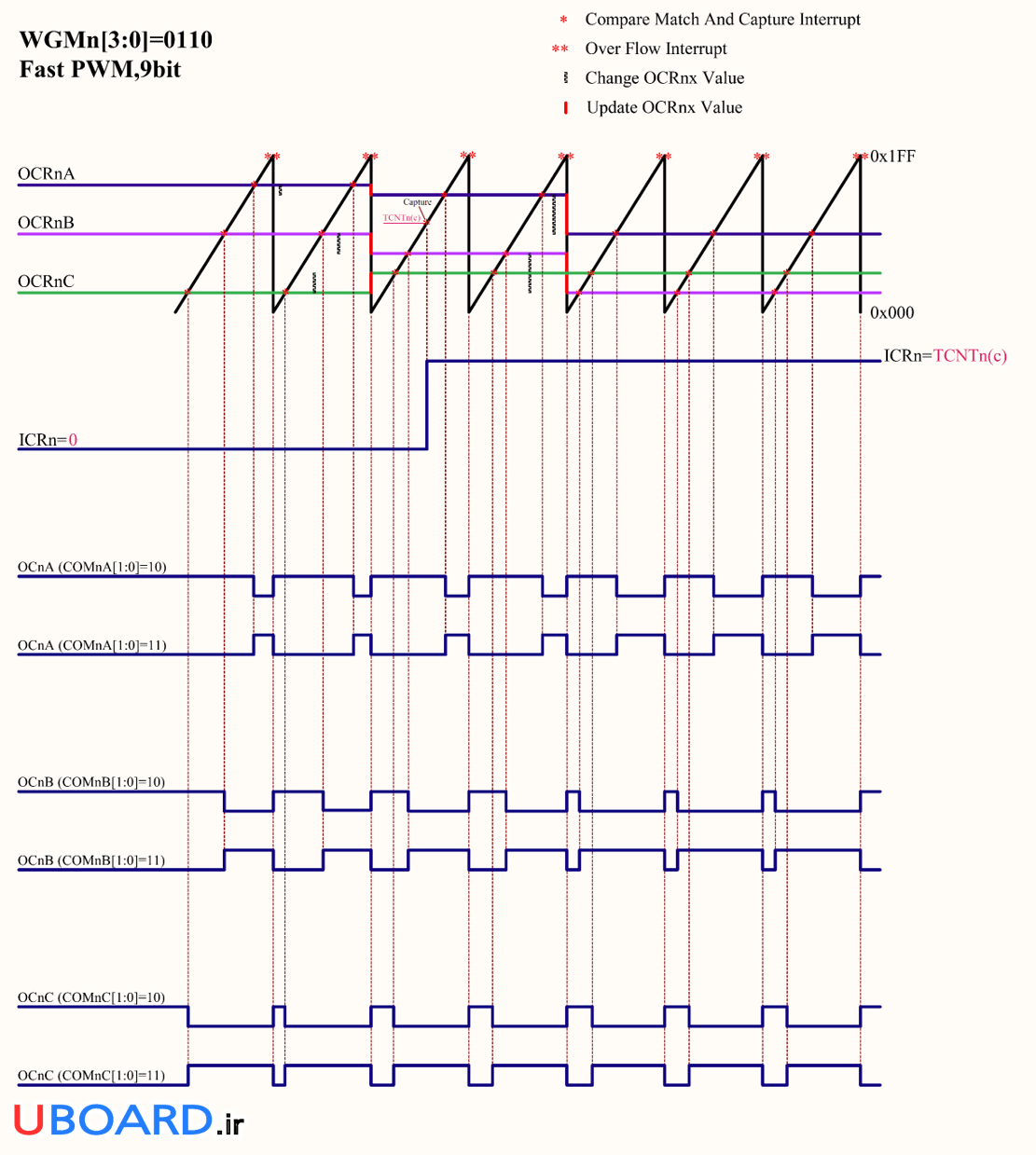

مد Fast PWM,9bit تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 6)

مشخصات مد PWM سریع 9 بیتی تایمر/کانتر در ATmega128A 1 و 3 به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| TOP | BOTTOM | 0x01FF | Fast PWM,9bit | 0 | 1 | 1 | 0 | 6 |

جدول 10 – مشخصات PWM سریع 9 بیتی تایمر/کانتر 1 و 3

عملکرد مد PWM سریع 9 بیتی شبیه مد شمارۀ 5 است. تنها تفاوت آن مقدار TOP است. مقدار تایمر در این مد تا 0x01FF بالا می رود.

تصویر 9 – نمودار زمانی مد PWM سریع 9 بیتی تایمر/کانتر 1 و 3 و شکل موج روی OCnx

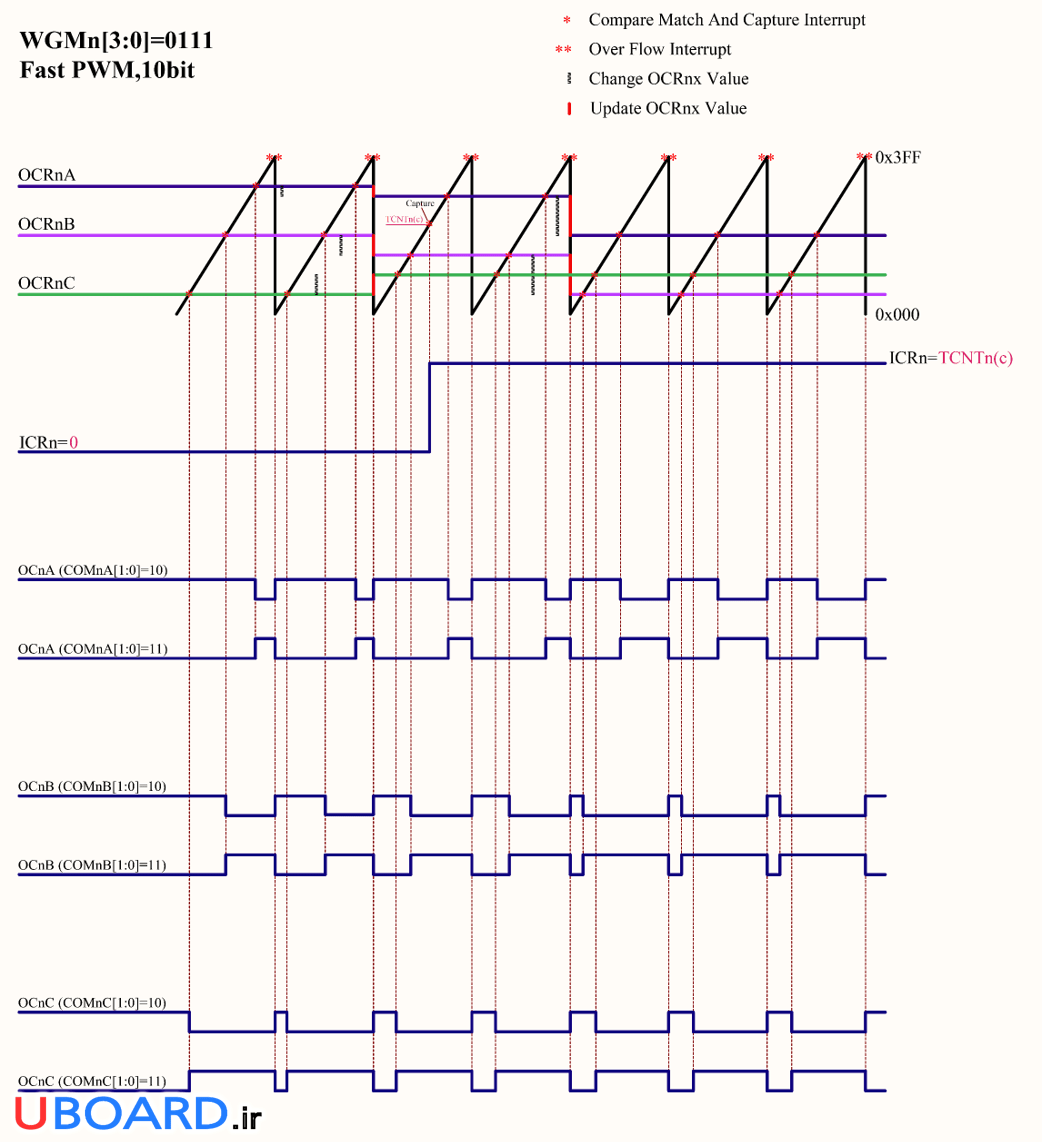

مد Fast PWM,10bit تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 7)

مشخصات مد PWM سریع 10 بیتی تایمر/کانتر 1 و 3 در ATmega128A به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| TOP | BOTTOM | 0x03FF | Fast PWM,10bit | 1 | 1 | 1 | 0 | 7 |

جدول 11 – مشخصات PWM سریع 10 بیتی تایمر/کانتر 1 و 3

عملکرد مد PWM سریع 10 بیتی شبیه مد شمارۀ 5 است. تنها تفاوت آن مقدار TOP است. مقدار تایمر در این مد تا 0x03FF بالا می رود.

تصویر 10 – نمودار زمانی مد PWM سریع 10 بیتی تایمر/کانتر 1 و 3 و شکل موج روی OCnx

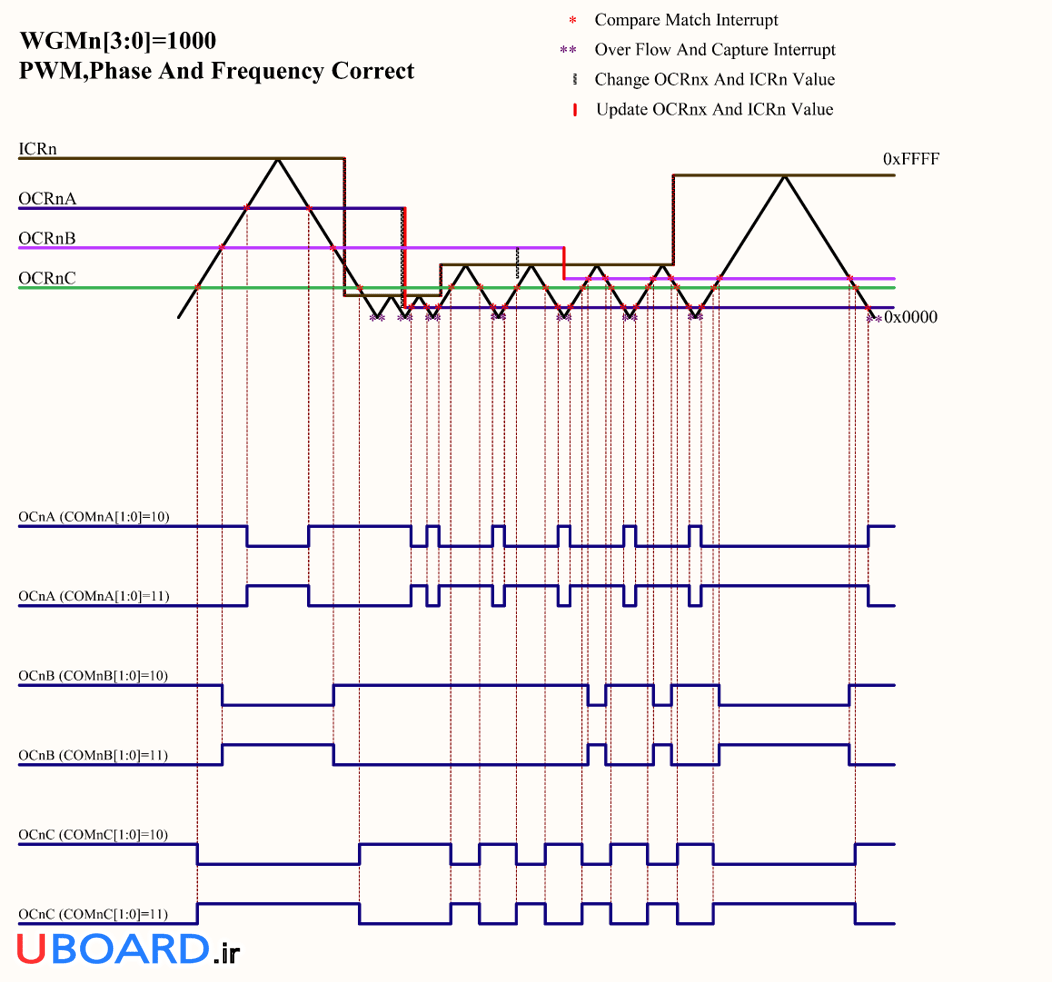

مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3 درATmega128A (مد شمارۀ 8):

مشخصات مد PWM,Phase and Frequency Correct تایمر/کانتر 1 و 3 در ATmega128A به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| BOTTOM | BOTTOM | ICRn | PWM,Phase and Frequency Correct | 0 | 0 | 0 | 1 | 8 |

جدول 12 – مشخصات مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3

توضیحات مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر تا مقدار رجیستر ICRn (که در برنامه مقدار دهی شده است) بالا می رود و سپس به صورت نزولی تا مقدار BOTTOM می شمارد. و دوباره جهت شمارش، صعودی می شود. (در این مد واحد capture قابل راه اندازی نیست.)

- مقدار TOP را رجیستر ICRn تعیین می کند. همچنین می توان OCRnA، OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM برای رجیسترهای مقایسۀ A، B و C اتفاق بیفتد، مقدار رجیسترهای OCRnA، OCRnB و OCRnC باید کمتر از ICRn باشد.

- در این مد هر جایی که رجیسترهای مقایسه مقدار دهی شوند مقدار آن ها در زمانی که تایمر به BOTTOM می رسد، در آن رجیسترها قرار می گیرد. و هر جایی که مقدار ICRn مقدار دهی شود این مقدار فوراً در آن رجیستر قرار می گیرد.

- سرریز وقتی اتفاق می افتد که مقدار تایمر (در حالی که جهت شمارش نزولی دارد) به BOTTOM برسد. هرگاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد.

- در این مد واحد capture تحریک نمی شود و می توان از پایۀ ICPn به عنوان یک پورت ورودی/خروجی استفاده کرد. مقدار نوشته شده در رجیستر ICRn نیز تعیین کنندۀ مقدار TOP است. همچنین در صورت فعال بودن وقفۀ capture، این وقفه زمانی اتفاق می افتد که مقدار تایمر به BOTTOM برسد. اولویت اتفاق افتادن وقفۀ capture نیز از وقفۀ سرریز بیشتر است و ابتدا وقفۀ capture اتفاق می افتد.

تصویر 11 – نمودار زمانی مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3 و شکل موج روی OCnx

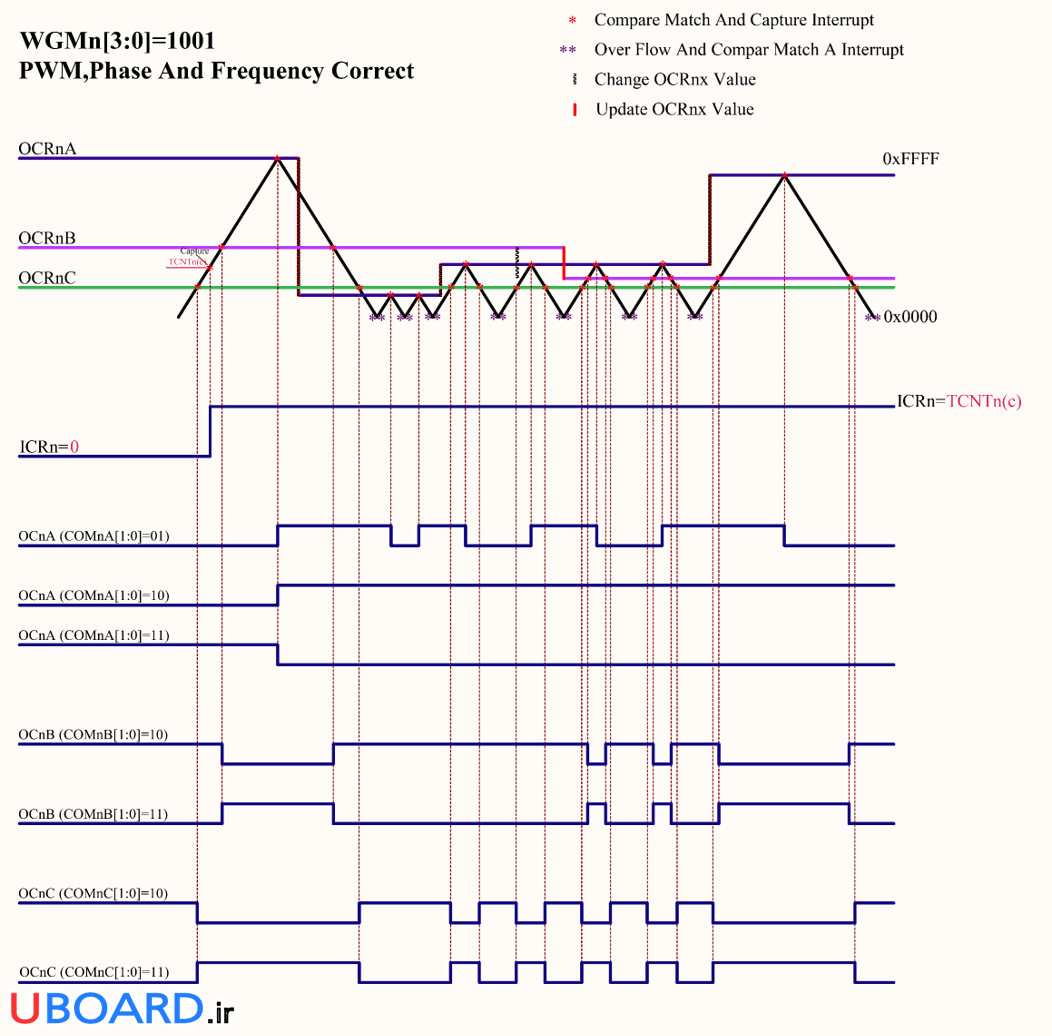

مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3 درATmega128A (مد شمارۀ 9):

مشخصات مد PWM,Phase and Frequency Correct تایمر/کانتر 1 و 3 در ATmega128A به صورت زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| BOTTOM | BOTTOM | OCRnA | PWM,Phase and Frequency Correct | 1 | 0 | 0 | 1 | 9 |

جدول 13 – مشخصات مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3

توضیحات مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3 در ATmega128A:

- این مد شبیه مد 8 است. تفاوت آنها با هم در مقدار TOP است.

- تایمر تا مقدار رجیستر OCRnA بالا می رود و سپس به صورت نزولی تا مقدار BOTTOM می شمارد. و دوباره جهت شمارش صعودی می شود.

- مقدار TOP را رجیستر OCRnA تعیین می کند. همچنین می توان OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM برای رجیسترهای مقایسۀ B و C اتفاق بیفتد، مقدار رجیسترهای OCRnB و OCRnC باید کمتر از OCRnA باشد.

- در این مد هر جایی که رجیسترهای مقایسۀ B و C مقدار دهی شوند مقدار آن ها در زمانی که تایمر به BOTTOM می رسد، در آن رجیسترها قرار می گیرد. و هر جایی که مقدار OCRnA مقدار دهی شود این مقدار فوراً در آن رجیستر قرار می گیرد.

- سرریز وقتی اتفاق می افتد که مقدار تایمر (در حالی که جهت شمارش نزولی دارد) به BOTTOM برسد. هرگاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد. همچنین در صورت فعال بودن وقفۀ مقایسۀ A، این وقفه زمانی اتفاق می افتد که مقدار تایمر به BOTTOM برسد. اولویت اتفاق افتادن وقفۀ مقایسۀ A از وقفۀ سرریز بیشتر است و ابتدا وقفۀ مقایسۀ A اتفاق می افتد.

- در این مد اگر واحد capture تحریک شود، مقدار تایمر در رجیستر ICRn ذخیره می شود و وقفۀ capture در صورت فعال بودن اتفاق می افتد. (ابتدا وقفه اتفاق می افتد سپس مقدار تایمر در رجیستر ICRn ذخیره می شود.)

تصویر 12 – نمودار زمانی مد PWM تصحیح فاز و فرکانس تایمر/کانتر 1 و 3 و شکل موج روی OCnx

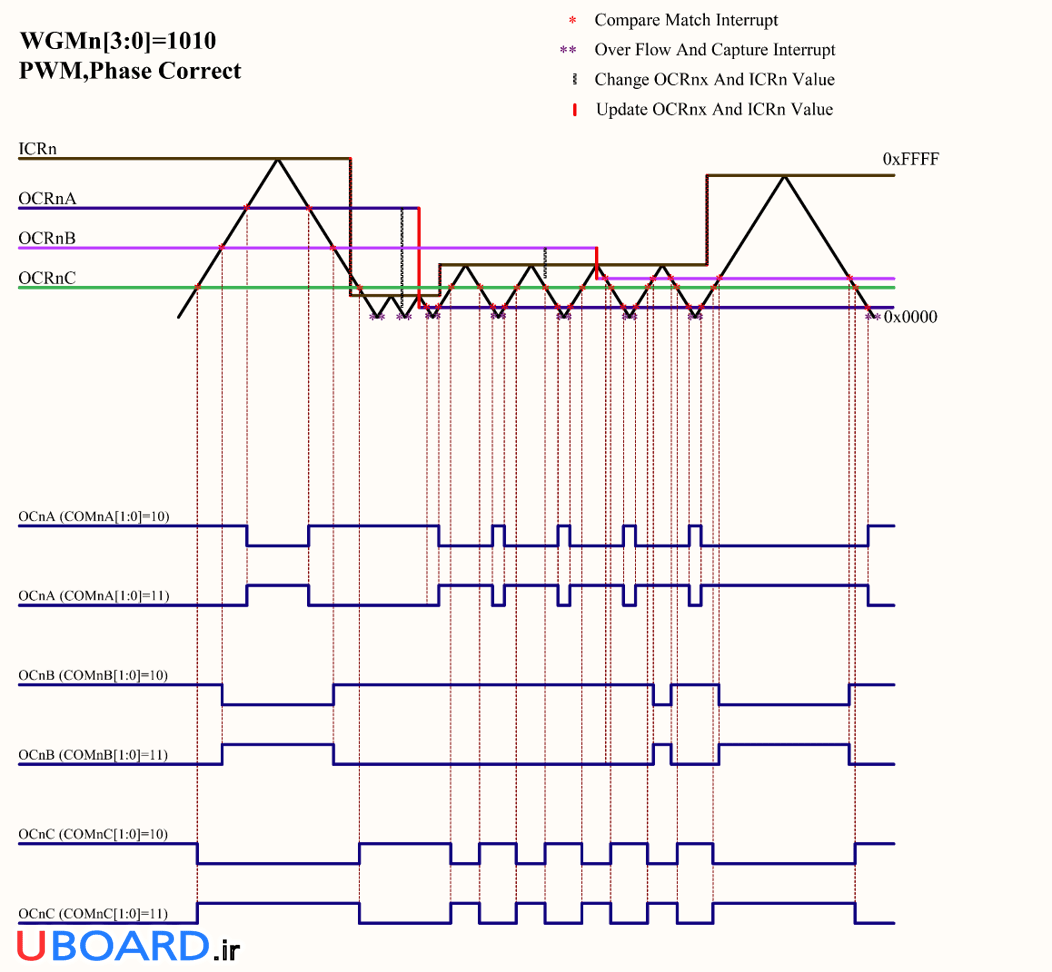

مد PWM تصحیح فاز تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 10):

در جدول زیر مشخصات مد PWM,Phase Correct تایمر/کانتر 1 و 3 در ATmega128A را مشاهده می کنید.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| BOTTOM | TOP | ICRn | PWM,Phase Correct | 0 | 1 | 0 | 1 | 10 |

جدول 14 – مشخصات مد PWM تصحیح فاز تایمر/کانتر 1 و 3

توضیحات مد PWM تصحیح فاز تایمر/کانتر 1 و 3 در ATmega128A:

- عملکرد این مد شبیه مد 8 است. با این تفاوت که در این مد زمان آپدیت شدن رجیسترهای OCRnx در TOP است.

- تایمر تا مقدار رجیستر ICRn (که در برنامه مقدار دهی شده است) بالا می رود و سپس به صورت نزولی تا مقدار BOTTOM می شمارد. و دوباره جهت شمارش، صعودی می شود. (در این مد واحد capture قابل راه اندازی نیست.)

- مقدار TOP را رجیستر ICRn تعیین می کند. همچنین می توان OCRnA، OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM برای رجیسترهای مقایسۀ A، B و C اتفاق بیفتد، مقدار رجیسترهای OCRnA، OCRnB و OCRnC باید کمتر از ICRn باشد.

- در این مد هر جایی که رجیسترهای مقایسه مقدار دهی شوند مقدار آن ها در زمانی که تایمر به TOP (مقدار قرار گرفته در ICRn) می رسد، در آن رجیسترها قرار می گیرد. و هر جایی که مقدار ICRn مقدار دهی شود این مقدار فوراً، در آن رجیستر قرار می گیرد.

- در این مد سرریز وقتی اتفاق می افتد که مقدار تایمر (در حالی که جهت شمارش نزولی دارد) به BOTTOM برسد. هرگاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد.

- در این مد واحد capture تحریک نمی شود و می توان از پایۀ ICPn به عنوان یک پورت ورودی/خروجی استفاده کرد. مقدار نوشته شده در رجیستر ICRn نیز تعیین کنندۀ مقدار TOP است. همچنین در صورت فعال بودن وقفۀ capture، این وقفه زمانی اتفاق می افتد که مقدار تایمر به BOTTOM برسد. اولویت اتفاق افتادن وقفۀ capture نیز از وقفۀ سرریز بیشتر است و ابتدا وقفۀ capture اتفاق می افتد.

تصویر 13 – نمودار زمانی مد PWM تصحیح فاز تایمر/کانتر 1 و 3 و شکل موج روی OCnx

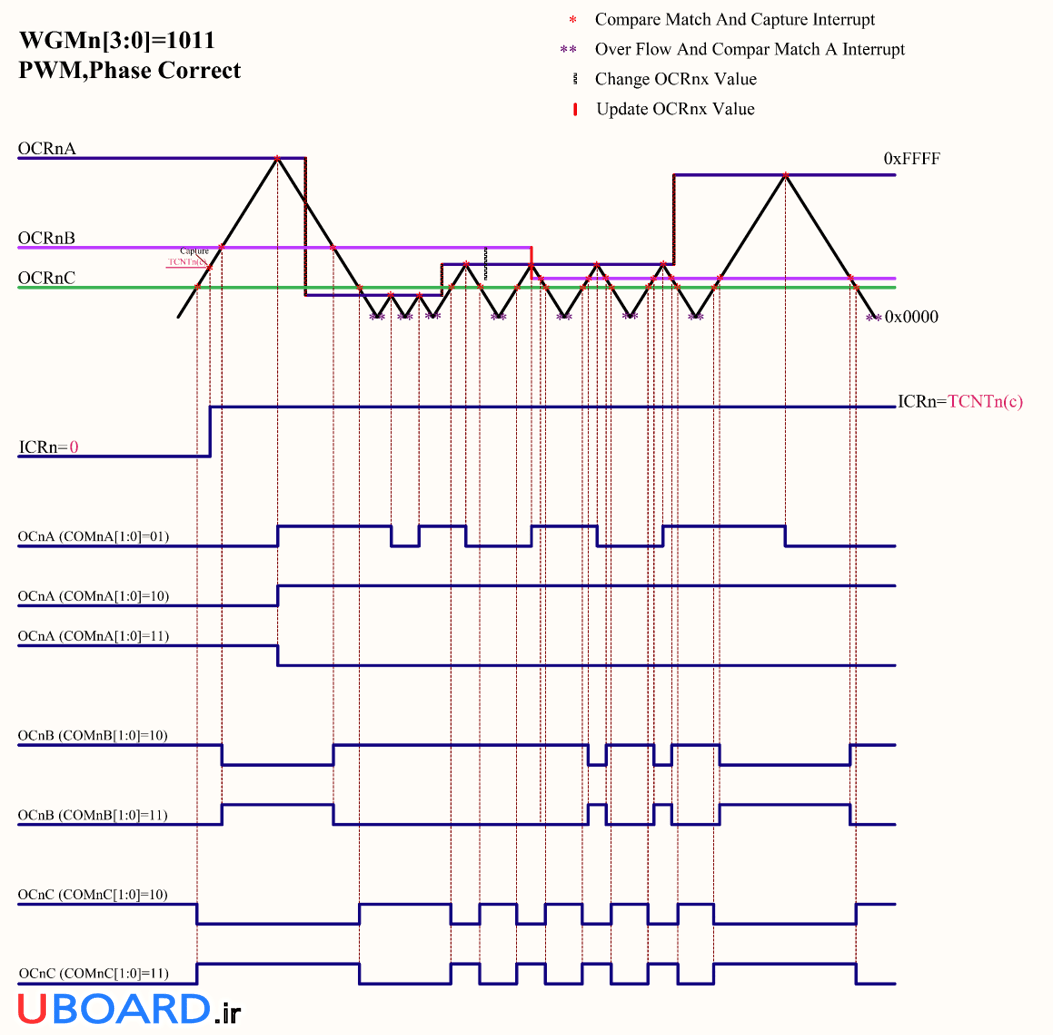

مد PWM تصحیح فاز تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 11):

مشخصات مد تصحیح فاز تایمر/کانتر 1 و 3 در ATmega128A به صورت جدول زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| BOTTOM | TOP | OCRnA | PWM,Phase Correct | 1 | 1 | 0 | 1 | 11 |

جدول 15 – مشخصات مد PWM تصحیح فاز تایمر/کانتر 1 و 3

توضیحات مد PWM تصحیح فاز تایمر/کانتر 1 و 3 در ATmega128A:

- عملکرد این مد شبیه مد 9 است. با این تفاوت که در این مد زمان آپدیت شدن رجیسترهای OCRnx در TOP است.

- تایمر تا مقدار OCRnA بالا می رود و سپس به صورت نزولی تا مقدار BOTTOM می شمارد. و دوباره جهت شمارش صعودی می شود.

- مقدار TOP را رجیستر OCRnA تعیین می کند. همچنین می توان OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM برای رجیسترهای مقایسۀ B و C اتفاق بیفتد، مقدار رجیسترهای OCRnB و OCRnC باید کمتر از OCRnA باشد.

- در این مد هر جایی که رجیسترهای مقایسه مقدار دهی شوند مقدار آن ها در زمانی که تایمر به TOP (مقدار قرار گرفته در OCRnA) می رسد، در آن رجیسترها قرار می گیرد. البته مقدار رجیستر OCRnA اگر تغییر کند فوراً در آن رجیستر قرار می گیرد.

- سرریز وقتی اتفاق می افتد که مقدار تایمر (در حالی که جهت شمارش نزولی دارد) به BOTTOM برسد. هرگاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد. همچنین در صورت فعال بودن وقفۀ مقایسۀ A، این وقفه زمانی اتفاق می افتد که مقدار تایمر به BOTTOM و OCRnA برسد. اولویت اتفاق افتادن وقفۀ مقایسۀ A از وقفۀ سرریز بیشتر است و ابتدا وقفۀ مقایسۀ A اتفاق می افتد.

- در این مد اگر واحد capture تحریک شود، مقدار تایمر در رجیستر ICRn ذخیره می شود و وقفۀ capture در صورت فعال بودن اتفاق می افتد. (ابتدا وقفه اتفاق می افتد سپس مقدار تایمر در رجیستر ICRn ذخیره می شود.)

تصویر 14 – نمودار زمانی مد PWM تصحیح فاز تایمر/کانتر 1 و 3 و شکل موج روی OCnx

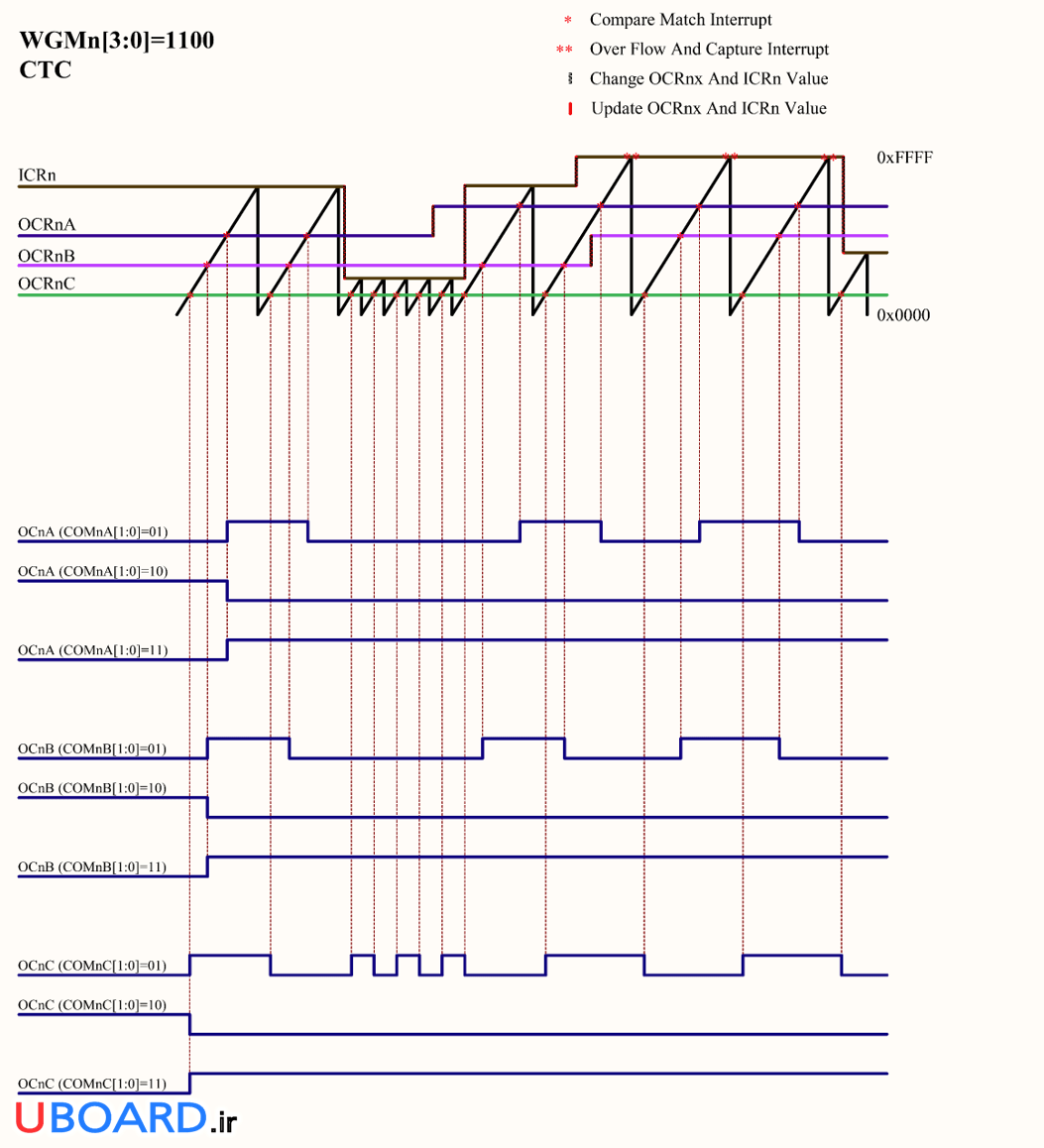

مد CTC تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 12):

مشخصات مد CTC تایمر/کانتر 1 و 3 در ATmega128A مطابق جدول زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| MAX | Immediate | ICRn | CTC | 0 | 0 | 1 | 1 | 12 |

جدول 16 – مشخصات مد CTC تایمر/کانتر 1 و 3

توضیحات مد CTC (Clear Timer on Compare) تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر تا مقدار رجیستر ICRn (که در برنامه مقدار دهی شده است) می شمارد و پس از آن به مقدار BOTTOM می رسد و دوباره از BOTTOM شروع به شمارش می کند. (در این مد واحد capture قابل راه اندازی نیست.)

- مقدار TOP را رجیستر ICRn تعیین می کند. همچنین می توان OCRnA، OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM ها اتفاق بیفتند، مقدار رجیسترهای OCRnA، OCRnB و OCRnC باید کمتر از ICRn باشد.

- مقادیر جدید برای رجیسترهای مقایسه فوراً در آنها قرار می گیرد. همچنین با تغییر رجیستر ICRn، مقدارِ جدید فوراً در آن قرار می گیرد.

- سرریز در MAX اتفاق می افتد و این امر تنها زمانی امکان پذیر است که ICRn=MAX (یعنی 0xFFFF) باشد. هر گاه تایمر سرریز شود وقفۀ سرریز در صورت فعال بودن اتفاق می افتد. و هر گاه CM اتفاق بیفتد وقفۀ مقایسۀ متناظر در صورت فعال بودن اتفاق می افتد.

- در این مد واحد capture تحریک نمی شود و می توان از پایۀ ICPn به عنوان یک پورت ورودی/خروجی استفاده کرد. مقدار نوشته شده در رجیستر ICRn نیز تعیین کنندۀ مقدار TOP است. همچنین در صورت فعال بودن وقفۀ capture، این وقفه زمانی اتفاق می افتد که مقدار تایمر به MAXبرسد. (یعنی باید مقدار ICRn برابر MAX باشد و وقتی تایمر به MAX برسد وقفۀ capture اتفاق می افتد.) اولویت اتفاق افتادن وقفۀ capture نیز از وقفۀ سرریز بیشتر است و ابتدا وقفۀ capture اتفاق می افتد.

تصویر 15 – نمودار زمانی مد CTC تایمر/کانتر 1 و 3 و شکل موج روی OCnx

مد شمارۀ 13 رزرو شده است.

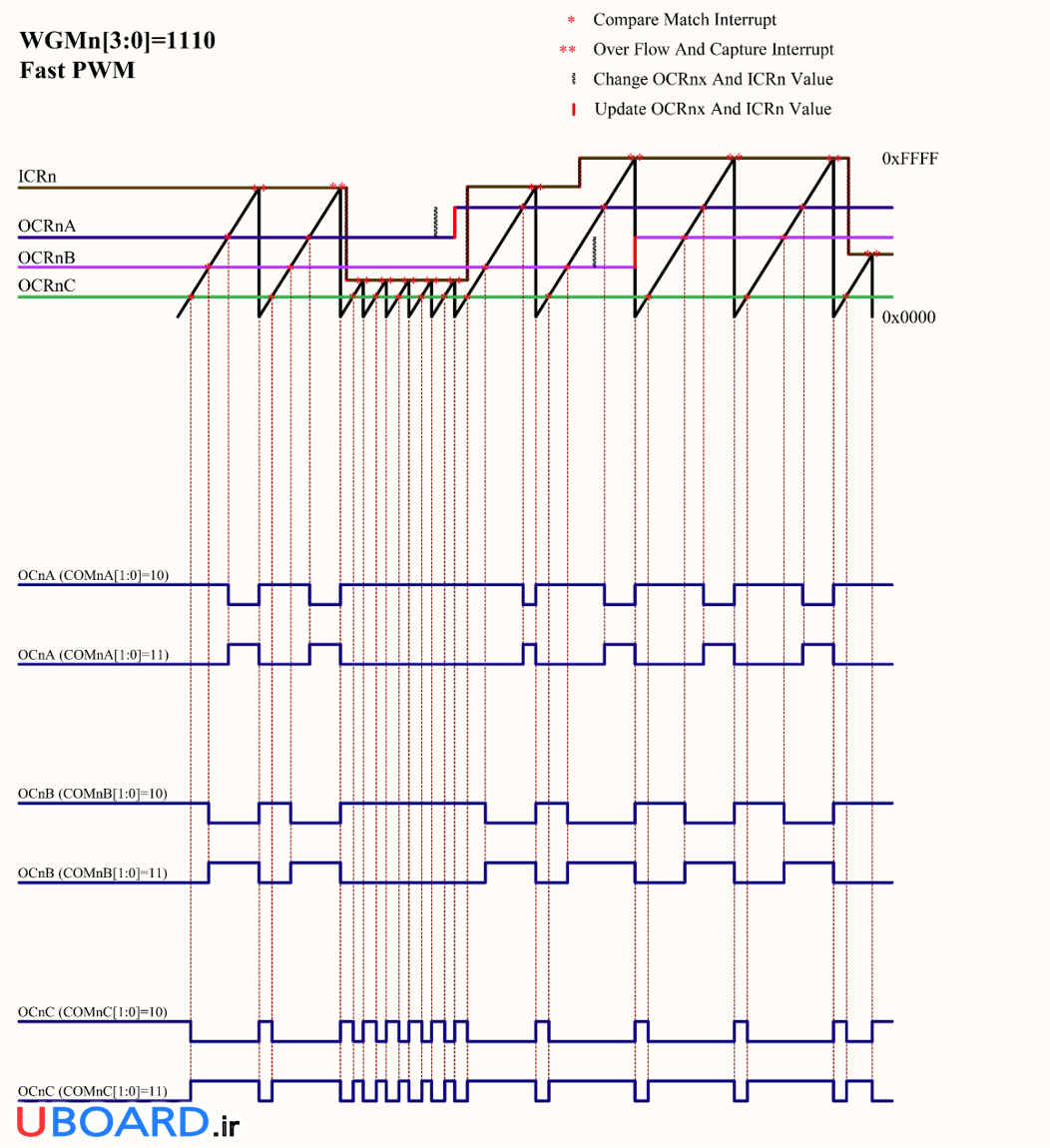

مد Fast PWM تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 14)

مشخصات مد PWM سریع تایمر/کانتر 1 و 3 در ATmega128A در جدول زیر آمده است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| TOP | BOTTOM | ICRn | Fast PWM | 0 | 1 | 1 | 1 | 14 |

جدول 17 – مشخصات مد PWM سریع تایمر/کانتر 1 و 3

توضیحات مد PWM سریع تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر تا مقدار ICRn (که در برنامه مقداردهی شده است) بالا می رود و پس از آن سرریز می شود و مقدارش به BOTTOM می رسد و دوباره از BOTTOM می شمارد.

- مقدار TOP را رجیستر ICRn تعیین می کند. همچنین می توان OCRnA، OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM ها اتفاق بیفتند، مقدار رجیسترهای OCRnA، OCRnB و OCRnC باید کمتر از ICRn باشد.

- هر جایی که رجیسترهای مقایسه مقدار دهی شوند این مقدار در زمانی که تایمر به BOTTOM برسد، در رجیسترهای مقایسه قرار داده می شوند. همچنین صورت تغییر مقدار ICRn، مقدار جدید فوراً در آن قرار می گیرد.

- در این مد سرریز درهنگام رسیدن مقدار تایمر به TOP است. یعنی هنگامی که مقدار تایمر به مقدار قرار گرفته در ICRn برسد، سرریز اتفاق می افتد. هرگاه وقفۀ سرریز فعال باشد، وقفۀ آن اتفاق می افتد و هرگاه هر یک از CMها اتفاق بیفتد و وقفۀ آن فعال باشد، وقفۀ CM اتفاق می افتد.

- در این مد واحد capture تحریک نمی شود و می توان از پایۀ ICPn به عنوان یک پورت ورودی/خروجی استفاده کرد. مقدار نوشته شده در رجیستر ICRn نیز تعیین کنندۀ مقدار TOP است. همچنین در صورت فعال بودن وقفۀ capture، این وقفه زمانی اتفاق می افتد که تایمر سرریز شود. اولویت اتفاق افتادن وقفۀ capture نیز از وقفۀ سرریز بیشتر است و ابتدا وقفۀ capture اتفاق می افتد.

تصویر 16 – نمودار زمانی مد Fast PWM تایمر/کانتر 1 و 3 و شکل موج روی OCnx

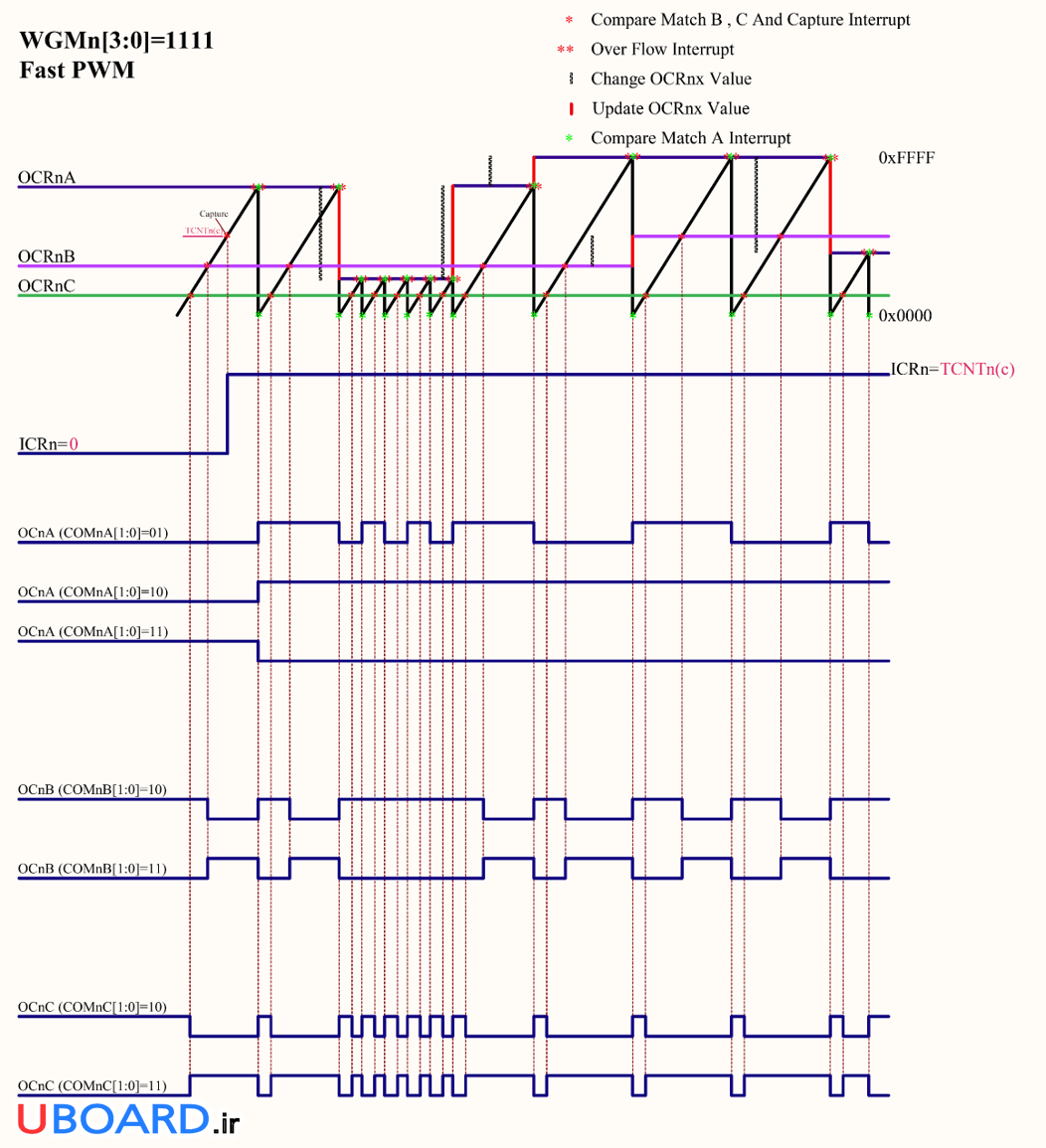

مد Fast PWM تایمر/کانتر 1 و 3 در ATmega128A (مد شمارۀ 15)

مشخصات مد PWM سریع تایمر/کانتر 1 و 3 در ATmega128A به صورت جدول زیر است.

| TOVn flag set on | Update of OCRnx at | TOP | Timer/Counter Mode Operation | WGMn0

(PWMn0) |

WGMn1

(PWMn1) |

WGMn2

(CTCn) |

WGMn3 | Mode |

| TOP | BOTTOM | OCRnA | Fast PWM | 1 | 1 | 1 | 1 | 15 |

جدول 18 – مشخصات مد PWM سریع تایمر/کانتر 1 و 3

توضیحات مد PWM سریع تایمر/کانتر 1 و 3 در ATmega128A:

- تایمر تا مقدار OCRnA بالا می رود و پس از آن سرریز می شود و مقدارش به BOTTOM می رسد و دوباره از BOTTOM می شمارد.

- مقدار TOP را رجیستر OCRnA تعیین می کند. همچنین می توان OCRnB و OCRnC را مقداردهی کرد و از خروجی های مقایسۀ آنها استفاده کرد. برای این که CM ها اتفاق بیفتند، مقدار رجیسترهای OCRnB و OCRnC باید کمتر از OCRnA باشد.

- هر جایی که رجیسترهای مقایسه مقدار دهی شوند این مقدار در زمانی که تایمر به BOTTOM می رسد، در رجیسترهای مقایسه قرار داده می شوند.

- در این مد سرریز درهنگام رسیدن مقدار تایمر به TOP است. یعنی هنگامی که مقدار تایمر به مقدار قرار گرفته در OCRnA برسد، سرریز اتفاق می افتد. هرگاه وقفۀ سرریز فعال باشد، وقفۀ آن اتفاق می افتد و هرگاه هر یک از CMها اتفاق بیفتد و وقفۀ آن فعال باشد، وقفۀ CM اتفاق می افتد. وقفۀ مقایسۀ A هم در هنگام سرریز اتفاق می افتد و هم در BOTTOM.

- در این مد اگر واحد capture تحریک شود، مقدار تایمر در رجیستر ICRn ذخیره می شود و وقفۀ capture در صورت فعال بودن اتفاق می افتد. (ابتدا وقفه اتفاق می افتد سپس مقدار تایمر در رجیستر ICRn ذخیره می شود.)

تصویر 17 – نمودار زمانی مد Fast PWM تایمر/کانتر 1 و 3 و شکل موج روی OCnx

چند نکته دربارۀ تایمر/کانتر 1 و 3:

- در همۀ مدهای تایمر/کانتر می توان در رجیستر TCNTn (مقدار تایمر) نوشت. در این صورت تایمر به محض دریافت مقدار TCNTn، از مقدار قرار گرفته در TCNTn شروع به شمارش می کند. این امر تنها برای یک بار قابل اجراست و پس از اولین سرریز (سرریز ممکن است در BOTTOM باشد)، تایمر طبق مد کاری خود شمارش می کند. برای این که همواره تایمر از مقدار معینی (به غیر از صفر) شروع به شمارش کند باید آن مقدار معین هنگام سرریز و در روتین وقفۀ سرریز یا در وقفه های دیگر در TCNTn نوشته شود. در این صورت تایمر همواره از مقدار قرار گرفته در TCNTn شروع به شمارش می کند و این امر تکرار می شود. در مدهایی که شمارش صعودی و نزولی داریم وقتی مقدار تایمر در حال افزایش است و مقداری به آن بدهیم، تایمر از آن مقدار به صورت صعودی می شمارد و وقتی شمارش تایمر نزولی است و مقداری به آن بدهیم تایمر از آن مقدار به صورت نزولی می شمارد.

- بیت های WGMn0، WGMn1 و WGMn2 به ترتیب نام های جدید بیت های PWMn0، PWMn1 و CTCn هستند.

- هر یک از واحدهای مقایسۀ A، B و C یک روتین وقفۀ جداگانه دارند.

- در تمام مدهای بالا منبع کلاک تایمر/کانتر می تواند از خارج از میکروکنترلر نیز باشد. یعنی برای کاربرد کانتر نیز می توان مدهای بالا را به کار برد.

- در مدهایی که ICRn و OCRnA تعیین کنندۀ مقدار TOP هستند، این رجیسترها باید بعد از بیت های WGMn[3:0]مقداردهی شوند.

- در نوشتن رجیسترهای 16 بیتی باید دقت کرد که ابتدا بایت پر ارزش نوشته شود سپس بایت کم ارزش و در هنگام خواندن آنها باید ابتدا بایت کم ارزش خوانده شود سپس بایت پر ارزش. برای مثال به رجیستر OCR1A مقدار می دهیم ومقدار رجیستر TCNT1 را میخوانیم و در متغیرهای TH و TL قرار می دهیم:

OCR1AH=0xFA;

OCR1AL=0xE5;

TL=TCNT1L;

TH=TCNT1H;

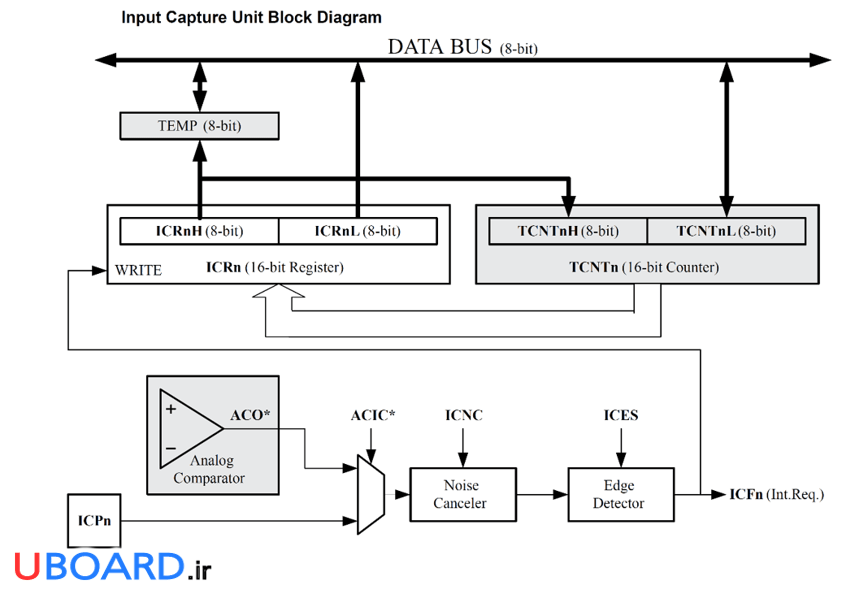

واحد Capture (تسخیر) در تایمر/کانتر 1 و 3

در مدهایی از تایمر 1 که رجیستر ICRn مقدار TOP را تعیین نمی کند، این واحد قابل استفاده است. عملکرد این واحد به این صورت است که با تحریک آن، مقدار فعلیِ تایمر (یا کانتر) در رجیستر ICRn ذخیره می شود. تحریک این واحد می تواند از دو منبع باشد:

- لبۀ بالا رونده یا پایین رونده روی پایۀ ICPn که نوع آن در رجیستر تعیین می شود؛

- خروجی مقایسه گر آنالوگ (ACO) که این منبع در رجیستر ACSR از رجیسترهای مقایسه گر آنالوگ تعیین می شود.

هر گاه یکی از این دو منبع واحد capture را تحریک کند، مقدار تایمر در رجیستر ICRn ذخیره می شود. در این واحد یک المان وجود دارد که با فعال سازی آن می توان عملکرد واحد capture را با استفاده از یک فیلتر دیجیتال ساده در برابر نویز ایمن کرد. این المان Noise Canceler نام دارد. با فعال سازی این المان، تعداد 4 نمونه از سیگنالی که روی پایۀ ICPn قرار دارد گرفته می شود. در صورت برابر بودن هر چهار نمونه، واحد capture تحریک می شود. المان noise canceler از کلاک cpu استفاده می کند، نه از فرکانس خروجی تقسیم کنندۀ فرکانس. استفاده از noise canceler باعث ایجاد تأخیر (به اندازۀ چهار کلاک cpu) در تحریک واحد capture می شود. که این تأخیر در مواردی که کلاک تایمر برابر کلاک cpu است، مقدار قابل توجهی است.

باید توجه داشت که اگر واحد capture قرار است چند بار پشت سر هم یا دائماً تحریک شود، مقدار رجیستر ICRn هر چه سریع تر خوانده شود. زیرا ممکن است تحریک بعدی پیش از خواندن مقدار ICRn، مقدار این رجیستر را تغییر دهد. برای این منظور وقفۀ capture بهترین زمان برای خواندن مقدار ICPn است. فواصل زمانی بین تحریک ها نیز باید به گونه ای باشد که این موضوع اتفاق نیفتد. همچنین استفاده از واحد capture در مدهایی که مقدار TOP دائماً در تغییر است توصیه نمی شود. شکل زیر بلوک دیاگرام واحد capture را نشان می دهد.

تصویر 18 – بلوک دیاگرام واحد Capture تایمر/کانتر 1 و 3 در AVR

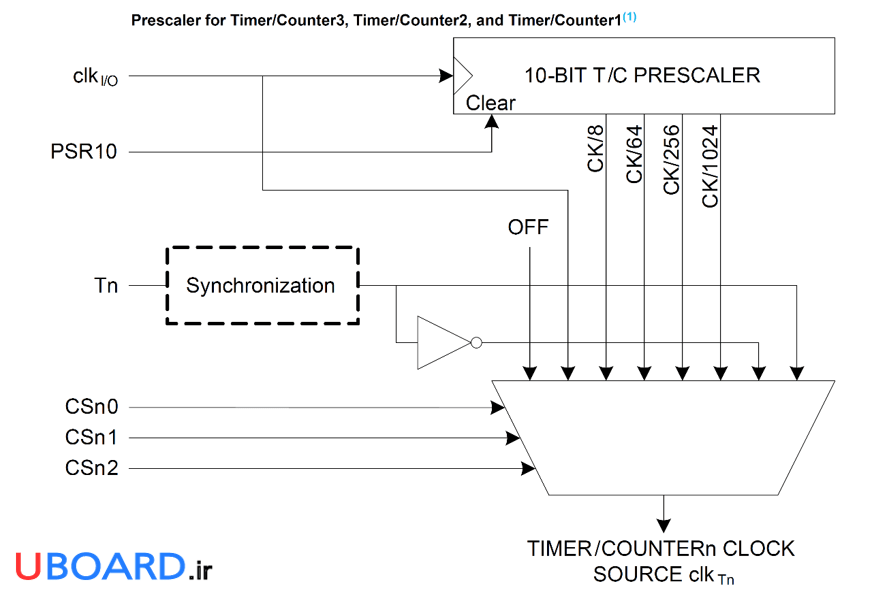

Prescaler در تایمر/کانتر 1 و 3

تایمر/کانتر 1 و 3 دارای یک واحد تقسیم کنندۀ فرکانس است که می تواند فرکانسِ cpu را به اعداد 8 و 64 و 256 و 1024 تقسیم کند و آنگاه آن را به تایمر بدهد. بلوک تایمر/کانتر می تواند با فرکانس cpu هم کار کند که در این صورت نیاز به تقسیم فرکانس نیست. همچنین در کاربرد کانتر، تقسیم کنندۀ فرکانس غیر قابل استفاده است. بلوک دیاگرام تقسیم کنندۀ فرکانس را در شکل زیر مشاهده می کنید.

تصویر 19 – بلوک دیاگرام واحد تقسیم کنندۀ فرکانس تایمر/کانتر 1 و 2 و 3

نوع کلاکِ بلوک تایمر/کانتر 1 و 3 با بیت های CSn[2:0] از رجیستر TCCRnB انتخاب می شود. اگر این سه بیت صفر باشند، تایمر/کانتر خاموش است، در غیر این صورت تایمر/کانتر فعال است و منبع کلاک آن با توجه به جدول زیر تعیین می شود.

| نوع کلاک تایمر/کانتر | CSn0 | CSn1 | CSn2 |

| تایمر/کانتر متوقف (خاموش) است. | 0 | 0 | 0 |

| کلاک cpu بدون تقسیم (clkI/O) | 1 | 0 | 0 |

| کلاک cpu تقسیم بر 8 (clkI/O/8) – از تقسیم کنندۀ فرکانس | 0 | 1 | 0 |

| کلاک cpu تقسیم بر 64 (clkI/O/64) – از تقسیم کنندۀ فرکانس | 1 | 1 | 0 |

| کلاک cpu تقسیم بر 256 (clkI/O/256) – از تقسیم کنندۀ فرکانس | 0 | 0 | 1 |

| کلاک cpu تقسیم بر 1024 (clkI/O/1024) – از تقسیم کنندۀ فرکانس | 1 | 0 | 1 |

| لبۀ پایین روندۀ سیگنال اعمالی به پایۀ Tn – سیگنال خارجی | 0 | 1 | 1 |

| لبۀ بالا روندۀ سیگنال اعمالی به پایۀ Tn – سیگنال خارجی | 1 | 1 | 1 |

جدول 19 – نوع کلاک تایمر/کانتر 1 و 3 در ATmega128A

کاربرد کانتر (Counter Mode) در تایمر/کانتر 1 و 3

همان طور که گفته شد اگر منبع کلاک بلوک تایمر/کانتر از بیرون از میکروکنترلر باشد، این بلوک در کاربرد کانتر قرار دارد. در این کاربرد بلوک تایمر/کانتر با هر لبۀ بالا رونده یا پایین روندۀ یک کلاک خارجی که روی پایۀ Tn اعمال می شود، کار می کند. با هر لبۀ بالا رونده یا پایین رونده، یک واحد به مقدار شمارش اضافه می شود. کاربرد کانتر در شمارشِ تعداد پالس های یک سیگنال است. این سیگنال می تواند از خرجی یک سنسور یا هر المان دیگری که نیاز به شمارش پالس های آن است، باشد. در کابرد کانتر نمی توان از تقسیم کنندۀ فرکانس استفاده کرد. همچنین بهتر است فرکانس سیگنال ورودی کانتر کمتر از 0.4 فرکانس cpu (یعنی 0.4 fclk_I/O) باشد. بلوک دیاگرام کانتر را در شکل زیر مشاهده می کنید.

تصویر 20 – بلوک دیاگرام کانتر 1 و 3 در ATmega128A

واحدهای مقایسۀ خروجی (Output Compare Units) یا واحد های مقایسه

تایمر/کانتر 1 و 3 در میکروکنترلر ATmega128 هر کدام دارای سه واحد مقایسه (یا واحد مقایسۀ خروجی) به نام های واحد مقایسۀ A، واحد مقایسۀ B و واحد مقایسۀ C هستند. این واحد های مقایسه دائماً مقدار خروجی تایمر را با رجیسترهای OCRnA، OCRnB و OCRnC (که در برنامه مقدار دهی شده اند) مقایسه می کنند و در صورت تطابق می توانند یک وقفه بدهند. هر یک از واحد های مقایسه دارای یک روتین وقفۀ جداگانه هستند. همچنین در هر یک از واحد های مقایسه یک بخش Waveform Generator وجود دارد که در صورت تطابق مقدار تایمر با مقدار رجیستر OCRnx می تواند خروجی واحد مقایسه (یعنی پایه های OCnx) را با توجه به مقادیر بیت های COMnx[1:0] صفر و یک کند. از این واحد می توان برای تولید موج PWM استفاده کرد. بلوک دیاگرام این واحد را در تصویر 2 مشاهده می کنید. همچنین بلوک دیاگرام خروجی واحد مقایسه را در شکل زیر می بینید.

تصویر 21 – بلوک دیاگرام خروجی واحد مقایسۀ تایمر/کانتر 1 و 3

مقایسۀ اجباری در تایمر/کانتر 1 و 3

در مدهایی به غیر از مدهای PWM (مدهای Normal و CTC)، با فعال سازی این بخش از واحدهای مقایسه، یک تطابق اجباری ایجاد می شود و با توجه به حالات خروجی مقایسه کننده ها یک تغییر سطح روی پایه های OCnx اتفاق می افتد. این تطابق اجباری تنها روی خروجی های واحد مقایسه اثر می گذارد و روی وقفه های آن اثر گذار نیست.

وقفه های تایمر کانتر 1 و 3

هر یک از بلوک های تایمر/کانتر 1 و 3، 5 وقفه دارند که با فعال کردن آنها می توان از روتین وقفۀ مربوطه برای نوشتن کدهای برنامه استفاده کرد. زمان اتفاق افتادن این وقفه ها به مد تایمر بستگی دارد. این 5 وقفه عبارتند از:

- وقفۀ سرریز؛

- وقفۀ capture؛

- وقفۀ مقایسۀ A؛

- وقفۀ مقایسۀ B؛

- وقفۀ مقایسۀ C.

رجیسترهای تایمر/کانتر 1 و 3

رجیسترهای تایمر/کانتر 1 و 3 دقیقاً شبیه هم هستند. در این رجیسترها n به معنای شمارۀ تایمر/کانتر (1 یا 3) و x بیانگر نام رجیستر مقایسه (A و B و C) است. این رجیسترها به شرح زیر می باشند:

رجیستر TCCR1A و TCCR1B و TCCR1C

این سه رجیستر کنترلی شامل بیت های WGM و COM است که حالات مختلف و مدهای مختلف با مقدار دهی به این رجیسترها حاصل می شوند. همچنین در این رجیسترها فرکانس کاری تایمر (مقدار تقسیم فرکانس از بلوک تقسیم فرکانس) یا کاربرد کانتر انتخاب می شود. در رجیستر سوم نیز بیت های مربوط به مقایسۀ اجباری قرار دارند که در ادامه توضیح داده می شوند.

| TCCRnA (Timer/Counter Control Register n A) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| WGMn0 | WGMn1 | COMnC0 | COMnC1 | COMnB0 | COMnB1 | COMnA0 | COMnA1 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 20 – رجیستر TCCRnA

| TCCRnB (Timer/Counter Control Register n B) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| CSn0 | CSn1 | CSn2 | WGMn2 | WGMn3 | – | ICESn | ICNCn | Bit name |

| R/W | R/W | R/W | R/W | R/W | R | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 21 – رجیستر TCCRnB

| TCCRnC (Timer/Counter Control Register n C) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| – | – | – | – | – | FOCnC | FOCnB | FOCnA | Bit name |

| R | R | R | R | R | W | W | W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 22 – رجیستر TCCRnC

بیت های WGMn[3:0](Waveform Generation Mode): این بیت ها تعیین کنندۀ مد عملیاتی تایمر/کانتر 1 و 3 است.

بیت های COMnx[1:0] (Compare Output Mode): این بیت ها حالت های خروجی مقایسه کننده های تایمر/کانتر 1 و 3 را تعیین می کنند.

بیت ICESn (Input Capture Edge Select): اگر این بیت صفر باشد، لبۀ پایین روندۀ سیگنال روی پایۀ ICPn واحد capture را تحریک می کند و اگر در این بیت 1 نوشته شود، لبۀ بالا روندۀ سیگنال روی پایۀ ICPn واحد capture را تحریک می کند.

بیت ICNCn (Input Capture Noise Canceler): با نوشتن 1 در این بیت، المان Noise Canceler فعال می شود و با نوشتن صفر در آن این المان غیر فعال می شود.

بیت های CSn[2:0] (Clock Select): این بیت ها تعیین کنندۀ نوع و مقدار کلاک تایمر/کانتر است.

بیت های FOCnx (Force Output Compare): با یک شدن هر یک از این بیت ها یک مقایسۀ اجباری برای مقایسه کنندۀ متناظر اتفاق می افتد.

رجیسترهای TCNTn (TCNTnL و TCNTnH)

مقدار تایمر در این رجیسترها قرار دارد. یعنی با هر کلاک به بلوک تایمر/کانتر یک واحد به این رجیستر اضافه می شود. این رجیسترِ 16 بیتی از دو رجیستر 8 بیتی تشکیل شده است.

| TCNTnL (Timer/Counter n Register Low Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| TCNTnL.0 | TCNTnL.1 | TCNTnL.2 | TCNTnL.3 | TCNTnL.4 | TCNTnL.5 | TCNTnL.6 | TCNTnL.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 23 – رجیستر TCNTnL

| TCNTnH (Timer/Counter n Register High Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| TCNTnH.0 | TCNTnH.1 | TCNTnH.2 | TCNTnH.3 | TCNTnH.4 | TCNTnH.5 | TCNTnH.6 | TCNTnH.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 24 – رجیستر TCNTnH

رجیسترهای OCRnAو OCRnB و OCRnC

این رجیسترها مربوط به واحد مقایسه هستند. در واحد مقایسه، مقدار تایمر با مقدار نوشته شده در این رجیسترها مقایسه می شود. هر کدام از این رجیسترهای 16 بیتی از دو رجیستر 8 بیتی تشکیل شده است.

| OCRnAL (Output Compare Register n A Low Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCRnAL.0 | OCRnAL.1 | OCRnAL.2 | OCRnAL.3 | OCRnAL.4 | OCRnAL.5 | OCRnAL.6 | OCRnAL.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 25 – رجیستر OCRnAL

| OCRnAH (Output Compare Register n A High Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCRnAH.0 | OCRnAH.1 | OCRnAH.2 | OCRnAH.3 | OCRnAH.4 | OCRnAH.5 | OCRnAH.6 | OCRnAH.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 26 – رجیستر OCRnAH

| OCRnBL (Output Compare Register n B Low Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCRnBL.0 | OCRnBL.1 | OCRnBL.2 | OCRnBL.3 | OCRnBL.4 | OCRnBL.5 | OCRnBL.6 | OCRnBL.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 27 – رجیستر OCRnBL

| OCRnBH (Output Compare Register n B High Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCRnBH.0 | OCRnBH.1 | OCRnBH.2 | OCRnBH.3 | OCRnBH.4 | OCRnBH.5 | OCRnBH.6 | OCRnBH.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 28 – رجیستر OCRnBH

| OCRnCL (Output Compare Register n C Low Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCRnCL.0 | OCRnCL.1 | OCRnCL.2 | OCRnCL.3 | OCRnCL.4 | OCRnCL.5 | OCRnCL.6 | OCRnCL.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 29 – رجیستر OCRnCL

| OCRnCH (Output Compare Register n C High Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCRnCH.0 | OCRnCH.1 | OCRnCH.2 | OCRnCH.3 | OCRnCH.4 | OCRnCH.5 | OCRnCH.6 | OCRnCH.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 30 – رجیستر OCRnCH

رجیستر ICRn (ICRnL و ICRnH)

این رجیستر مربوط به واحد capture است. هر گاه واحد capture تحریک شود مقدار تایمر که در رجیستر TCNTn قرار دارد در رجیستر ICRn ذخیره می شود.

| ICRnL (Input Capture Register n Low Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| ICRnL.0 | ICRnL.1 | ICRnL.2 | ICRnL.3 | ICRnL.4 | ICRnL.5 | ICRnL.6 | ICRnL.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 31 – رجیستر ICRnL

| ICRnH (Input Capture Register n High Byte) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| ICRnH.0 | ICRnH.1 | ICRnH.2 | ICRnH.3 | ICRnH.4 | ICRnH.5 | ICRnH.6 | ICRnH.7 | Bit name |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | Access |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Initial Value |

جدول 32 – رجیستر ICRnH

رجیستر TIMSK

بیت های 2 تا 5 این رجیستر مربوط به وقفه های تایمر/کانتر 1 است.

| TIMSK (Timer/Counter Interrupt Mask Register) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| TOIE1 | OCIE1B | OCIE1A | TICIE1 | Bit name | ||||

| R/W | R/W | R/W | R/W | Access | ||||

| 0 | 0 | 0 | 0 | Initial Value | ||||

جدول 33 – رجیستر TIMSK در تایمر/کانتر 1 و 3

بیت TICIE1 (Timer/Counter 1 Input Capture Interrupt Enable): با یک شدن این بیت، وقفۀ capture برای تایمر/کانتر 1 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت OCIE1A (Timer/Counter 1 Output Compare A Match Interrupt Enable): با یک شدن این بیت، وقفۀ مقایسۀ A برای تایمر/کانتر 1 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت OCIE1B (Timer/Counter 1 Output Compare B Match Interrupt Enable): با یک شدن این بیت، وقفۀ مقایسۀ B برای تایمر/کانتر 1 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت TOIE1 (Timer/Counter 1 Overflow Interrupt Enable): با یک شدن این بیت، وقفۀ سرریز برای تایمر/کانتر 1 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

رجیستر ETIMSK

بیت صفر این رجیستر مربوط به وقفۀ مقایسۀ C تایمر/کانتر 1 و بیت های 1 تا 5 آن نیز مربوط به وقفه های تایمر/کانتر 3 می باشد.

| ETIMSK (Extended Timer/Counter Interrupt Mask Register) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCIE1C | OCIE3C | TOIE3 | OCIE3B | OCIE3A | TICIE3 | Bit name | ||

| R/W | R/W | R/W | R/W | R/W | R/W | Access | ||

| 0 | 0 | 0 | 0 | 0 | 0 | Initial Value | ||

جدول 34 – رجیستر ETIMSK

بیت TICIE3 (Timer/Counter 3 Input Capture Interrupt Enable): با یک شدن این بیت، وقفۀ capture برای تایمر/کانتر 3 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت OCIE3A (Timer/Counter 3 Output Compare A Match Interrupt Enable): با یک شدن این بیت، وقفۀ مقایسۀ A برای تایمر/کانتر 3 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت OCIE3B (Timer/Counter 3 Output Compare B Match Interrupt Enable): با یک شدن این بیت، وقفۀ مقایسۀ B برای تایمر/کانتر 3 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت TOIE3 (Timer/Counter 3 Overflow Interrupt Enable): با یک شدن این بیت، وقفۀ سرریز برای تایمر/کانتر 3 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت OCIE3C (Timer/Counter 3 Output Compare C Match Interrupt Enable): با یک شدن این بیت، وقفۀ مقایسۀ C برای تایمر/کانتر 3 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

بیت OCIE1C (Timer/Counter 1 Output Compare C Match Interrupt Enable): با یک شدن این بیت، وقفۀ مقایسۀ C برای تایمر/کانتر 1 فعال می شود و با صفر شدن آن، این وقفه غیر فعال می شود.

رجیستر TIFR

در این رجیستر پرچم های مربوط به وقفه های تایمر/کانتر 1 قرار دارد.

| TIFR (Timer/Counter Interrupt Flag Register) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| TOV1 | OCF1B | OCF1A | ICF1 | Bit name | ||||

| R/W | R/W | R/W | R/W | Access | ||||

| 0 | 0 | 0 | 0 | Initial Value | ||||

جدول 35 – رجیستر TIFR

بیت ICF1 (Timer/Counter 1 Input Capture Flag): با اتفاق افتادن وقفۀ capture برای تایمر/کانتر 1، این پرچم 1 می شود.

بیت OCF1A (Timer/Counter 1 Output Compare A Match Flag): با اتفاق افتادن وقفۀ مقایسۀ A برای تایمر/کانتر 1، این پرچم 1 می شود.

بیت OCF1B (Timer/Counter 1 Output Compare B Match Flag): با اتفاق افتادن وقفۀ مقایسۀ B برای تایمر/کانتر 1، این پرچم 1 می شود.

بیت TOV1 (Timer/Counter 1 Overflow Flag): با اتفاق افتادن وقفۀ سرریز برای تایمر/کانتر 1، این پرچم 1 می شود.

رجیستر ETIFR

بیت صفر این رجیستر، پرچم وقفۀ مقایسۀ C برای تایمر/کانتر 1 و بیت های 1 تا 5 آن نیز پرچم وقفه های تایمر/کانتر 3 می باشد.

| ETIFR (Extended Timer/Counter Interrupt Flag Register) | ||||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | Bit number |

| OCF1C | OCF3C | TOV3 | OCF3B | OCF3A | ICF3 | Bit name | ||

| R/W | R/W | R/W | R/W | R/W | R/W | Access | ||

| 0 | 0 | 0 | 0 | 0 | 0 | Initial Value | ||

جدول 36 – رجیستر ETIFR

بیت ICF3 (Timer/Counter 3 Input Capture Flag): با اتفاق افتادن وقفۀ capture برای تایمر/کانتر 3، این پرچم 1 می شود.

بیت OCF3A (Timer/Counter 3 Output Compare A Match Flag): با اتفاق افتادن وقفۀ مقایسۀ A برای تایمر/کانتر 3، این پرچم 1 می شود.

بیت OCF3B (Timer/Counter 3 Output Compare B Match Flag): با اتفاق افتادن وقفۀ مقایسۀ B برای تایمر/کانتر 3، این پرچم 1 می شود.

بیت TOV3 (Timer/Counter 3 Overflow Flag): با اتفاق افتادن وقفۀ سرریز برای تایمر/کانتر 3، این پرچم 1 می شود.

بیت OCF3C (Timer/Counter 3 Output Compare C Match Flag): با اتفاق افتادن وقفۀ مقایسۀ C برای تایمر/کانتر 3، این پرچم 1 می شود.

بیت OCF1C (Timer/Counter 1 Output Compare C Match Flag): با اتفاق افتادن وقفۀ مقایسۀ C برای تایمر/کانتر 1، این پرچم 1 می شود.

چند تمرین برای تایمر/کانتر 1 و 3

از آنجا که راه یادگیری تایمر/کانتر در میکروکنترلرها با تمرین هموارتر می شود، تمرین هایی در این زمینه طرح کرده ایم. آموزش تایمر AVR نیز با طرح تمرین ساده تر خواهد بود. این تمرین ها ساده هستند ولی پله ای برای درک عمیق مبحث تایمر/کانتر بسیار مفیدند. فایل های برنامه و شبیه سازی این تمرین ها در پیوست موجود است.

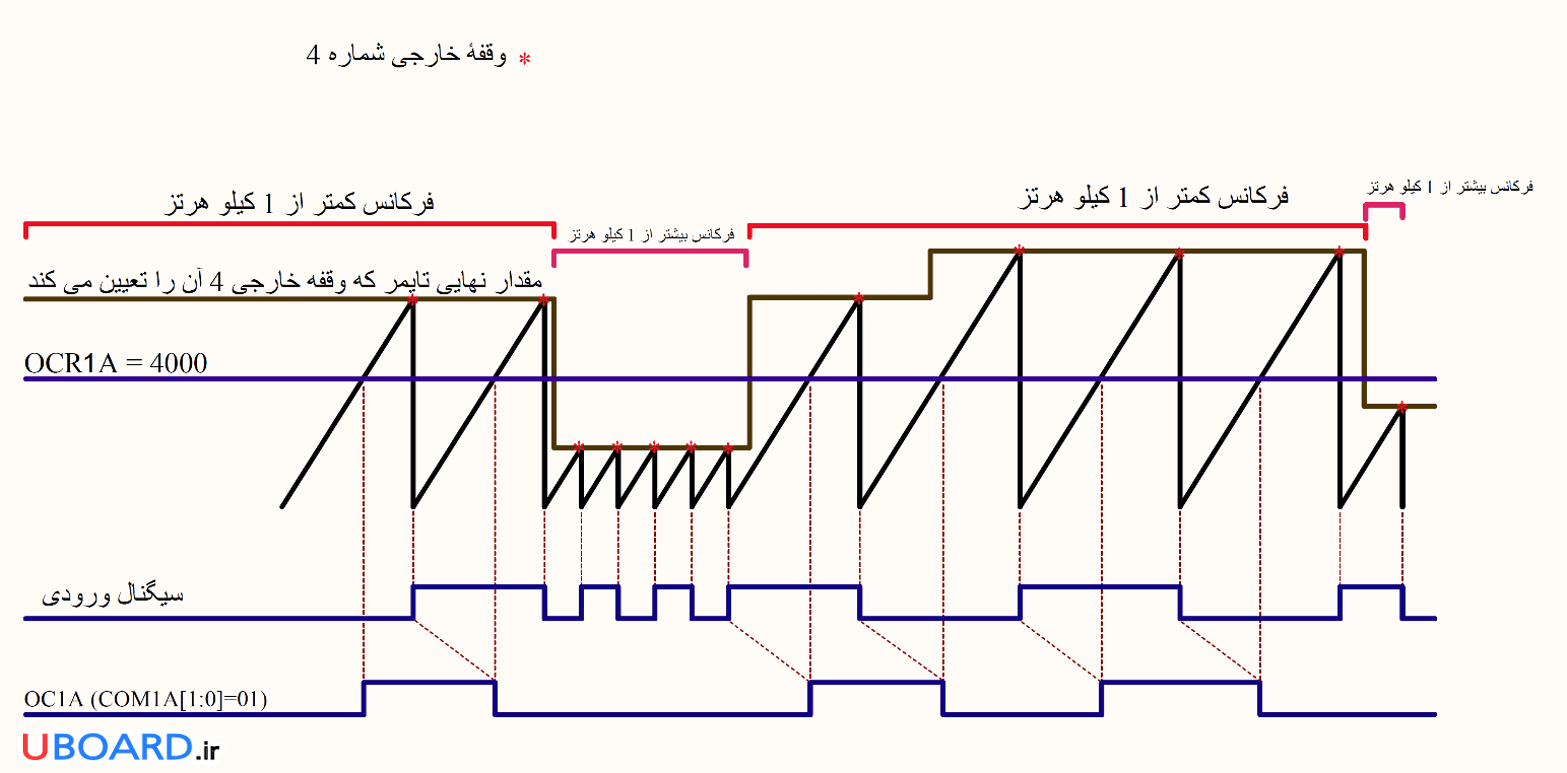

تمرین 1: عبوردهندۀ سیگنال با فرکانس زیر 1kHz با تایمر/کانتر 1 و 3

یک سیگنال پالسی شکل به پایۀ INT4 اعمال می شود که فرکانس آن بین 200 Hz تا 5 kHz تغییر می کند. با استفاده از مد صفر تایمر یک و استفاده از وقفۀ خارجی شمارۀ چهار (با حساسیت به هر دو لبۀ بالا رونده و پایین رونده) برنامه ای بنویسید که سیگنال ورودی با فرکانس های کمتر از 1 kHz (از 200 Hz تا 1 kHz) را به پایۀ OC1A انتقال دهد. فرکانس کاری میکروکنترلر را 8 MHz قرار دهید و فرکانس کاری تایمر یک همان 8 MHz باشد. برنامۀ تایمر با کدویژن نوشته شود.

راهنمایی: زمان هر پله از تایمر برابر 1/8M = 0.125us است. و پریود یک سیگنال 1 kHz برابر 1000 us می باشد. برای این که یک سیگنال با فرکانس 1 kHz روی پایۀ OC1A داشته باشیم باید رجیستر OCR1A برابر 4000 باشد و مقدار تایمر تا عدد 4000 بالا برود و پس از آن تایمر صفر شود و دوباره این سیکل تکرار شود. هر بار که تایمر به مقدار 4000 می رسد خروجی OC1A یک بار تغییر وضعیت می دهد (حالت toggle برای OC1A، یعنی COM1A[1:0]=01 باشد). پس پریود سیگنال خروجی که حاصل دو تغییر وضعیت OC1A است، برابر 8000 پلۀ تایمر می باشد که زمان آن برابر 8000 * 0.125 = 1000 us می شود. حال برای این که فقط فرکانس های کمتر از 1 KHz از میکروکنترلر عبور کند باید مقدار OCR1A برابر 4000 باشد و ما در وقفۀ خارجی شمارۀ چهار مقدار تایمر را صفر کنیم. در این صورت تایمر تا زمانی که وقفه اتفاق می افتد بالا می رود و سپس صفر می شود. حال اگر مقدار تایمر کمتر از 4000 باشد مقایسۀ A اتفاق نمی افتد و خروجی آن toggle نمی شود. ولی اگر مقدار تایمر بالاتر از 4000 باشد خروجی OC1A همواره toggle می شود و همان سیگنال با همان فرکانس به خروجی منتقل می شود. در این برنامه هدفِ استفاده از وقفه آن است که در آن وقفه، مقدار تایمر را صفر کنیم. و این وقفه حتماً باید حساس به هر دو لبه باشد.

تصویر 22 – انتقال سیگنال زیر یک کیلو هرتز به پایۀ OC1A

تمرین 2: ساخت موج مربعی با فرکانس بین 100 هرتز تا 4 کیلوهرتز

با استفاده از مد شماره 4 تایمر/کانتر یک، یک تولید کنندۀ پالس با فرکانس متغیر بین 100 Hz تا 4 kHz بسازید. فرکانس کاری میکروکنترلر و تایمر یک هر دو 8 MHz باشد.

راهنمایی: OC1A را در حالت toggle قرار دهید و مقدار OCR1A را بین دو عدد بگیرید تا محدودۀ فرکانسی مورد نظر بدست بیاید. پایه های PD.0 و PD.1 را ورودی می کنیم. قرار است با فشردن کلید روی PD.0 فرکانس زیاد شود و با فشردن کلید روی PD.1 فرکانس کم شود. تایمر با پله های 0.125 میکرو ثانیه ای تا مقدار OCR1A بالا می رود. در این هنگام با قرار دادن OC1A روی حالت toggle پایۀ OC1A تغییر وضعیت می دهد. حال باید محاسبه کنیم که مقدار OCR1A برای فرکانس های 100Hz و 4kHz چقدر است. پریود سیگنال 100Hz برابر 10000 میکرو ثانیه است. برای تولید این شکل موج OC1A باید هر 5000 میکرو ثانیه یک بار تغییر وضعیت دهد. پس مقدار OCR1A باید برابر 5000/0.125 = 40000 باشد. به همین صورت برای فرکانس 4kHz پریود سیگنال برابر 250 میکرو ثانیه است. برای تولید این شکل موج باید تایمر تا مقدار 125 بالا برود و OCR1A یک بار تغییر وضعیت بدهد. بنابراین مقدار OCR1A برابر است با 125/0.125 = 1000 باشد. برنامه را طوری می نویسیم که با هر بار فشردن کلیدهای روی PD.0 و PD.1، 500 واحد از OCR1A کم شود و یا به آن اضافه شود. مقدار دهی به رجیستر 16 بیتی نیز باید رعایت شود و ابتدا باید OCR1AH مقداردهی شود و سپس OCR1AL.

تمرین 3: ساخت فرکانس متر دیجیتال با رنج اتوماتیک با استفاده از کاربرد کانتر

در این تمرین که می تواند یک پروژۀ تایمر با AVR باشد، قصد داریم با استفاده از مد صفر تایمر/کانتر یک، یک فرکانس متر با رنج اتوماتیک بسازیم. برنامه به این صورت است که برای تعیین رنج چند حلقۀ while بی نهایت تعریف شده است. برنامه قرار است در یک زمان مشخص (delay) تعداد پالس هایی را که به پایۀ T1 (پایۀ PD.6 از میکروکنترلر ATmega128) اعمال می شود بشمارد. برای این کار در ابتدای هر حلقه، کانتر 1 روشن می شود و بعد از یک delay دوباره خاموش می شود. مقدار شمارش شده از رجیستر TCNT1 خوانده می شود. همچنین یک مقدار دیگر (i) هم خوانده می شود. i مقداری است که در اثر سرریز کانتر 1 بدست آمده است. هر بار که کانتر 1 سرریز می شود در روتینِ وقفۀ سرریزِ کانتر 1، به i یک واحد اضافه می شود. مقدار TCNT1 با مقدار i*65536 جمع می شود که کل زمان مورد نظر ما را در بر می گیرد. اگر تعداد پالس های شمارش شده بر زمان مورد نظر تقسیم شود فرکانس بدست می آید. در این برنامه از مد صفر تایمر/کانتر 1 استفاده شده است.

حلقۀ اول (رنج 1000Hz)

در این حلقه ابتدا کانتر 1 روشن می شود. سپس یک delay برابر 1000ms ایجاد می شود. بعد از این delay مقدار شمارش شدۀ پالس (TCNT1) و تعداد دفعات سرریز (i) خوانده می شوند. همچنین مقدار i در عدد 65536 ضرب می شود تا تعداد پالس های شمارش شده در یک چرخۀ کامل سرریز بدست بیاید. در سطر بعدی TCNT1 و تعداد پالس حاصل از سرریزها (i) با هم جمع می شوند تا تعداد پالس های شمرده شده (F) در 1000ms بدست بیاید. حال کانتر 1 خاموش می شود. در مرحلۀ بعد F که همان فرکانس است روی LCD نمایش داده میشود. بعد از نمایش F، مقدار i و TCNT1 صفر می شوند تا دوباره در چرخۀ دیگر حلقۀ بی نهایت اندازه گیری شوند.

TCCR1A=(0<<COM1A1) | (0<<COM1A0) | (0<<COM1B1) | (0<<COM1B0) | (0<<WGM11) | (0<<WGM10);

TCCR1B=(0<<ICNC1) | (0<<ICES1) | (0<<WGM13) | (0<<WGM12) | (1<<CS12) | (1<<CS11) | (0<<CS10);

delay_ms(1000);

F=TCNT1/1.0;

i=i*65536.0;

F=F+i;

TCCR1A=(0<<COM1A1) | (0<<COM1A0) | (0<<COM1B1) | (0<<COM1B0) | (0<<WGM11) | (0<<WGM10);

TCCR1B=(0<<ICNC1) | (0<<ICES1) | (0<<WGM13) | (0<<WGM12) | (0<<CS12) | (0<<CS11) | (0<<CS10);

lcd_clear();

sprintf(str,"RANGE:1000Hz\nf = %.0f Hz",F);

lcd_puts(str);

delay_ms(50);

TCNT1=0;

i=0;

سطر اول و دوم: روشن شدن کانتر

سطر سوم: delay برابر با 1 ثانیه

سطر چهارم: خواندن مقدار TCNT1 و قرار دادن آن در متغیر F و همچنین تبدیل آن به متغیر نوع float

سطر پنجم: خواندن تعداد دفعات سرریز و ضرب آن در تعداد پالس یک چرخۀ کامل کانتر (65536)

سطر ششم: جمع پالس های حاصل از سرریز و پالس های شمارش شده در تایمر قبل از سرریز و قرار دادن آن در F

سطر هفتم و هشتم: خاموش کردن کانتر 1

سطر نهم و دهم و یازدهم: نمایش F در LCD کاراکتری

سطر دوازدهم: ایجاد یک delay برای نمایش روی LCD

سطر سیزدهم و چهاردهم: بازگرداندن i و TCNT1 به مقدار اولیه یعنی صفر.

رنج اتوماتیک

برای این که فرکانس در محدودۀ وسیعی اندازه گیری شود لازم است تا delay در محدوده های دیگر به کار گرفته شود. برای این منظور چند حلقۀ بی نهایت دیگر تعریف شده اند تا در صورتی که رنج فرکانس عوض شد، برنامه به حلقه های دیگر پرش کند و کدهای آن حلقه را اجرا کند.

برای رنج 1000Hz از delay برابر با 1000ms استفاده شده است.

برای رنج 10kHz از delay برابر با 500ms استفاده شده است.

برای رنج 100kHz از delay برابر با 500ms استفاده شده است.

برای رنج 1MHz از delay برابر با 10ms استفاده شده است.

برای رنج 8MHz از delay برابر با 1000µs استفاده شده است.

برای این که از خاصیت Auto Range استفاده کنیم لازم است در هر حلقۀ بی نهایت مقدار فرکانس در محدودهی رنج خود سنجیده شود. به طوری که اگر فرکانس در آن رنج نباشد برنامه به حلقه ای پرش کند که آن فرکانس را در بر می گیرد. در برنامه رنج ها به ترتیب قرار گرفته اند. در انتهای هر حلقۀ بی نهایت دو شرط (if) تعریف شده است که فرکانس را می سنجند. اگر فرکانس از محدودۀ رنجِ در حالِ اجرا کمتر باشد، برنامه به رنج قبلی پرش می کند. و اگر فرکانس بیشتر از محدودۀ رنجِ این حلقه باشد برنامه به رنجِ بعدی که محدوده ای با فرکانس بالاتر است پرش می کند. مثلاً در حلقۀ بی نهایت سوم که رنج فرکانس محدودۀ 100kHz می باشد، اگر فرکانس کمتر از 10kHz باشد برنامه به حلقۀ قبلی پرش می کند و اگر فرکانس بزرگتر از 100kHz باشد به حلقۀ بعدی که رنج بالاتر است پرش می کند.

if ((F>100)&(j==7)){

goto range4;

}

if ((F<=10)&(j==7)){

goto range2;

}

در ابتدای هر حلقه یک برچسب زده شده است که وقتی در انتهای حلقه ها این دو شرط بررسی می شوند برنامه به برچسب مورد نظر پرش کند. برای این منظور از دستور goto استفاده میشود.

range1 , range2 , range3 , range4 , range5

لازم به ذکر است که این فرکانس متر در تئوری تا فرکانس 8MHz را اندازه می گیرد. اما بنا به مطالب دیتاشیت، بهتر است فرکانس اعمال شده به کانتر کمتر از 0.4 فرکانس کاری CPU (یعنی 3.2MHz) باشد.

تمرین 4: تولید سه موج PWM با استفاده از تایمر/کانتر 3

با استفاده از مد 6 تایمر/کانتر سه، سه شکل موج PWM بسازید و با 6 کلید عرض پالس آنها را بین 1 تا 254 پله از تایمر تغییر دهید. فرکانس کاری میکروکنترلر 8 MHz و فرکانس کاری تایمر 1 MHz باشد. راه اندازی تایمر در کدویژن انجام شود.

راهنمایی: 6 پایۀ اول پورت D را ورودی با پول آپ داخلی می کنیم. 6 کلید روی این پورت ها قرار می دهیم و سر دیگر کلیدها را به زمین وصل می کنیم. تایمر سه را روی مد 6 می گذاریم. هر سه خروجی آن را فعال می کنیم و روی PWM ناوارون تنظیم می کنیم. همچنین با تنظیم بیت های CS به صورت CS3[2:0]=010 فرکانس cpu را به 8 تقسیم می کنیم تا فرکانس کاری تایمر 1 MHz شود. برای هر کلید شرط می نویسیم که به مقادیر OCR3xL اضافه یا از آن کم شود.

از آموزش تایمر/کانتر 1 و 3 نتایج زیر حاصل می شوند:

- بلوک های تایمر/کانتر در AVR یا 8 بیتی هستند یا 16 بیتی.

- تایمر/کانتر 1 و 3 در ATmega128A هم تایمر است و هم کانتر. تایمر/کانتر 1 و شبیه همدیگر هستند.

- در هر کدام از مدهای تایمر/کانتر حالت هایی برای تغییر وضعیت OCnx وجود دارد. این حالات با بیت های COMnx1 و COMnx0 انتخاب می شوند.

- تایمر/کانتر 1 و 3 دارای چهارده مد است که شامل مدهای نرمال، PWM تصحیح فاز، PWM تصحیح فاز و فرکانس، PWM سریع و CTC می شوند.

- مد شمارۀ 13 رزرو شده است. یعنی برای این مد عملکردی تعریف نشده است.

- اگر به رجیستر TCNTn مقدار بدهیم، تایمر/کانتر از آن مقدار شروع به شمارش می کند.

- بیت های WGMn0 و WGMn1 و WGMn2 به ترتیب نام های جدید بیت های PWMn0 و PWMn1 و CTCn هستند.

- هر کدام از واحدهای مقایسۀ A و B و C، یک روتین وقفۀ جداگانه دارند.

- در مدهایی که ICRn و OCRnA تعیین کنندۀ مقدار TOP هستند، این رجیسترها باید بعد از مقداردهی به بیت های WGMn[3:0] مقداردهی شوند.

- در نوشتن رجیسترهای 16 بیتی ابتدا باید بایت پرارزش نوشته می شود.

- در خواندن رجیسترهای 16 بیتی باید ابتدا بایت کم ارزش خوانده شود.

- واحد Capture در مدهایی که رجیستر ICRn مقدار TOP را مشخص نمی کند قابل استفاده است.

- واحد Capture می تواند توسط دو منبع تحریک شود: 1- لبۀ بالا رونده یا پایین روندۀ سیگنال روی پایۀ ICPn؛ 2- خروجی مقایسه گر آنالوگ.

- یک المان Noise Canceler در واحد Capture وجود دارد که با استفاده از 4 نمونه برداری از سیگنال روی پایۀ ICPn، از تحریک واحد Capture توسط نویز جلوگیری می کند.

- در استفاده از Noise Canceler در مواردی که فرکانس تایمر/کانتر برابر با فرکانس CPU است، در ذخیره کردن مقدار تایمر/کانتر در رجیستر ICRn تأخیر قابل توجهی ایجاد می کند.

- برای راه اندازی تایمر/کانتر کافی است بیت های CSn[2:0] برابر 000 نباشند.

- در کاربرد کانتر در تایمر/کانتر 1 و 3، کلاک از پایۀ T1 و T3 گرفته می شود. این کلاک نمی تواند با واحد تقسیم فرکانس تقسیم بر عددی شود و مستقیماً به تایمر/کانتر وصل می شود.

- مقایسۀ اجباری در مدهای نرمال و CTC وجود دارد. با مقایسۀ اجباری وقفۀ مقایسه اتفاق نمی افتد.

- فرکانس سیگنال ورودی به پایۀ T1 و T3 در کاربرد کانتر بهتر است کمتر از 4 فرکانس کلاک CPU باشد. یعنی کمتر از 0.4fclk_I/O باشد.

- با توجه به 16 بیتی بودن تایمر/کانتر 1 و 3، رجیسترهای TCNTn و OCRnx و ICRnنیز 16 بیتی هستند.

- در راه اندازی تایمر 1 و 3 در مدهایی که ICRn و OCRnA مقدار TOP را تعیین می کنند، توجه شود که این رجیسترها پس از بیت های WGMn[3:0] مقداردهی شوند.

سلام مهندس اسدی. من زیاد با تایمرها کار نکردم.یعنی کلا تجربه زیادی توی میکروکنترلرها ندارم. شنیدم که دقت تایمرهای ۸ بیتی کمه و امروزه خیلی از مواقع به تایمرهای ۱۶ بیتی نیاز داریم. این حرف چقدر درسته؟

سلام. این که یه تایمر دقتش بالا باشه یا پایین به تعداد بیت های اون بستگی نداره. به فرکانس کلاک تایمر بستگی داره. شما فرض کنید میخواید یه فاصلۀ زمانی رو بسازید. مثلاً میخواید هر n میلی ثانیه یک بار یه کاری انجام بشه. ساختن این n میلی ثانیه هم به فرکانس کلاک تایمر بستگی داره و هم به تعداد بیت های تایمر. چیزی توی دقت زمان n میلی ثانیه دخالت داره فرکانس کلاک تایمر هستش. فرض کنید فرکانس کلاک تایمر 1 مگاهرتز باشه. با این توصیف زمان هر پله از تایمر 1 میکروثانیه س. حالا ما اگه بخوایم زمان 100 میکروثانیه بسازیم، میشه ساخت. 100 پله از تایمر میشه 100 میکروثانیه. حالا میتونیم زمان 112.25 میکروثانیه بسازیم؟ نه نمیتونیم. چون هر پله از تایمر 1 میکروثانیه است. حالا اگه فرکانس تایمر رو بالا ببریم دقت اون هم زیاد میشه. فرض کنید فرکانس تایمر رو 4 مگا هرتز انتخاب کنیم. الان هر پله از تایمر دارای زمان 0.25 میکروثانیه س. الان اگه بخوایم زمان 112.25 میکروثانیه رو بسازیم باید اون رو تقسیم بر 0.25 کنیم تا تعداد پله های تایمر به دست بیاد. که میشه 449 تا پله. ولی یه تایمر 8 بیتی تا 255 بیشتر نمیتونه بشمره و بعد از اون سرریز میشه. برای حل این مشکل از تایمر 16 بیتی استفاده می کنن. نتیجه میگیریم که دقت تایمر به فرکانس کلاک تایمر بستگی داره و نه تعداد بیت های تایمر. حالا اگه ما یه زمانی رو بخوایم با تایمر بسازیم که نیاز باشه تعداد پله های بیشتر از 255 تا رو بشمره، از تایمرهای 16 بیتی (یا تعداد بیت های بیشتر) استفاده می کنیم. در واقع دلیل اصلی استفاده از تایمر با تعداد بیت های بیشتر، دست یابی به زمان های طولانی تره. برای این که متوجه بشید زمانی که با تایمر میسازیم به چه کاری میاد میتونید نوشتۀ «تولید موج سینوسی با آی سی DAC0800 و میکروکنترلر AVR با فرکانس متغیر» رو مطالعه کنید. که توی اون از تایمر برای ساختن زمان های ثابت استفاده شده.

سلام استاد

اولا بخاطر روش تدریس عالی و نوع گزارش نویسی و جزوه نوشتن که بسیار مفید و قابل استفاده هست به جنابعالی و تیم فنی یوبورد تبریک میگویم و امیدوارم همیشه موفق باشید.

ثانیا در این مقاله یک تمرین بسیار خوبی در صفحه 57 ( تمرین 1 ) وجود دارد که بنام عبور دهنده سیگنال با فرکانس زیر 1KHz است ، سوال من اینست که اگر ممکنه راهنمایی بفرمایید چطور میتوانم برنامه ای برای عبور سیگنال با فرکانس بین دو فرکانس f1 و f2 بنویسم.

باز هم از راهنمایی های شما سپاسگزارم.

سلام مهندس

میکرو کنترلر atmega 64 دو تا تایمر 16 بیتی داره درست.

داخل کدویژن از TCNT1 میشه استفاده کرد ولی برای استفاده از TCNT3 یعنی کل 16 بیت (TCNT3L & TCNT3H) باید چه دستور اسمبلی زد تا بتونم از 16 بیت استفاده کنیم ؟؟؟

مشکل خیلی از کاربراس

ممنون میشم راهنمایی کنید

سلام. دوست عزیز دستور اسمبلی که این کار رو انجام بده اطلاعی ندارم. البته سعی کردم توی فایل mega64a.h تغییراتی بدم. خواستم عبارات sfrw TCNT3=0x88 رو وارد کنم که بعد از کامپایل ارور داد. بعد از اون این کار رو کردم. دیفاین زیر رو به اول فایل main اضافه کردم:

#define TCNT3 (*(unsigned int *) 0x88)

این دیفاین مطابق الگوی دیفاین رجیسترها توی فایل mega64a.h هستش. بعد توی برنامه به جای TCNT3L و TCNT3H نوشتم TCNT3. و توی پروتئوس چک کردم. مقادیر مختلف به TCNT3 از 8 بیتی تا 16 بیتی دادم. توی شبیه سازی درست کار کرد. در واقع از مد نرمال استفاده کردم و OC3A رو روی حالت Toggle گذاشتم. با تغییر مقادیر TCNT3، مقدار فرکانس موج خروجی درست و برابر با مقادیر تئوری بودن. دیگه تست نکردم ببینم با این روش مقدار رجیسترای دیگه تحت تأثیر قرار میگیره یا نه. این مورد رو خودتون زحمتش رو بکشید.

سلام و عرض ادب خدمت مهندس اسدی، ممنون از متن آموزشی و عالی شما. بنده قصد دارم که شکل موج PWM سه فاز تولید کنم. به نظر شما برای این کار از بردهای آردواینو استفاده کنم یا مستقیما از میکروکنترلر AVR و مثلا همین مدل ATmega128A یا هر مدل دیگری که تایمر آن امکانات کافی داشته باشد؟ در صورتی که مورد دوم را تایید می فرمایید، لطفا بفرمایید برای کار کردن مستقیم با میکروکنترلر چه تجهیزات سخت افزاری باید فراهم نمایم؟ از توجّه شما سپاسگزارم. غلامحسین نقی زاده

سلام. خیلی ممنون. لطف دارید. برای ساخت شکل موج PWM سه فاز هم میتونید از آردوینو استفاده کنید و هم از میکروکنترلر. اما کاش مشخصات این موج PWM هم میگفتید تا ببینیم اصلا میشه این کار با AVR انجام بشه یا نه. مثلا اگه فرکانس های بالا بخواید نمیشه یه شکل موج PWM درآورد که دیوتی سایکل اون رو با دقت مناسب تغییر داد. حالا این که از آردوینو استفاده کنید یا نه، به نظرم بیشتر به خودتون بستگی داره. آردوینو راحت تره و سریع تر شما رو به نتیجه میرسونه. میتونه برای نمونه اولیه خوب باشه. اگه بخواید از میکروکنترلرها استفاده کنید میتونید از ATmega64A یا ATmega128A یا هر AVR دیگه ای که تایمری با سه خروجی PWM داره، استفاده کنید. برای این کار باید علاوه بر میکروکنترلر این قطعات و وسایل هم داشته باشید:

پروگرمر AVR که پروگرمرهای MK2 و USBasp و STK500 و … موجود هست.

رگولاتور ولتاژ. در صورتی که تغذیۀ کل مثلاً 12 ولته باید با رگولاتور، تغذیۀ میکروکنترلر رو فراهم کنید. مثل رگولاتور LM7805 یا رگولاتور سوییچینگ LM2576 یا رگولاتورهای دیگه. که هر کدوم یه مدار خارجی دارن که توی دیتاشیت اونا گفته شده که چه قطعاتی لازم دارن

درصورتی که بخواید با شکل موج PWM یه المانی رو راه اندازی کنید، مثلاً یه موتور، باید درایور موتور بسازید یا اگه موجود هست، بخرید.

و قطعات جانبی خود میکروکنترلر مثل سلف و خازن و مقاومت و کریستال و …

حالا اگه میگفتید دقیقاً میخواید چی کار کنید بهتر میتونستم راهنماییتون کنم. موفق باشید